# Design and Evaluation of a Cellular Rectifier System With Distributed Control

David J. Perreault, Member, IEEE, and John G. Kassakian, Fellow, IEEE

*Abstract*— This paper presents the design and experimental evaluation of a six-cell 6-kW cellular (parallel) rectifier system which operates at nearly unity power factor. The cellular rectifier system implements both distributed load sharing and distributed ripple cancellation, eliminating the need for any centralized control. The implemented system mitigates some of the major drawbacks of its single-converter counterpart and achieves performance levels that cannot be achieved with an equivalent single converter.

*Index Terms*—Cellular architecture, current sharing, interleaving, paralleled converters, single-switch boost rectifier, switchedmode rectifier.

#### I. INTRODUCTION

**O**NE APPROACH to constructing a large power converter, such as a switched-mode rectifier, is the use of a cellular converter architecture, in which many quasiautonomous power converters, called *cells*, are paralleled to form the equivalent of a single large converter [1]–[3]. The cell power rating is selected such that the cells can be constructed using inexpensive high-volume components and fabricated using automated manufacturing techniques. The use of quasi-autonomous cells means that system operation is not compromised in the event of the failure of a cell.

The cellular architecture has several potential advantages over conventional methods of constructing power converter systems, including performance, reliability, and cost [2]. Performance advantages arise from the ability to achieve a high degree of ripple cancellation among the cells and also from reductions in the power stage interconnection parasitics. Reliability advantages come from the ability to employ the natural redundancy of a parallel converter system, as well as from the use of highly reliable automated manufacturing and test procedures. The cellular architecture does have some cost liabilities due to the fact that some components, such as sensing and control elements, must be replicated among cells. However, there are also some cost benefits to the approach, including the reduction of labor costs due to the use of automated manufacturing techniques, and the simplification of the thermal management system which is possible due to the distribution of heat generation. Through proper design, it

The authors are with the Laboratory for Electromagnetic and Electronic Systems, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: djperrea@mit.edu).

Publisher Item Identifier S 0278-0046(99)04128-3.

should be possible to achieve cost parity or even a net cost benefit using a cellular architecture.

To fully realize these advantages, however, it is necessary to develop appropriate design and control methodologies and experimentally establish their viability at a reasonable power level. While the cellular architecture is well suited to many power conversion functions, it is particularly advantageous for the design of switched-mode rectifiers. Furthermore, the increasing importance of input power quality (and the advent of regulations and recommendations governing it [4]–[6]) make improved rectification techniques important for many commercial and industrial applications. For these reasons, we have applied the cellular conversion approach to the task of high-power-factor switched-mode rectification.

This paper describes the design, implementation, and experimental evaluation of a six-cell 6-kW cellular rectifier system. Power is converted from the three-phase 208-V mains to a 410-V dc output at nearly unity power factor. The cellular rectifier system implements both distributed load sharing and distributed ripple cancellation, eliminating the need for any centralized control. Furthermore, the cellular converter system mitigates some of the major drawbacks of its single-converter counterpart and achieves performance levels unattainable with an equivalent single converter.

Section II describes some of the motivations for the use of a cellular architecture in rectifier applications and provides an introduction to the cell topology used in the prototype system. Section III quantifies the effects of interleaving the cells on the aggregate input current ripple. Section IV describes the design of the prototype system, including the system architecture and the power stage, while Section V describes the control design, including the output voltage controller, the loadsharing control system, and the ripple cancellation control system. Section VI provides experimental results from the laboratory prototype, and Section VII draws conclusions and presents a preliminary evaluation of the approach.

#### II. SWITCHED-MODE RECTIFICATION

The emergence of recent standards and recommendations on power quality reflect a growing need to reduce the impact of electronic equipment on the utility. While only voluntary measures, such as IEEE Std 519-1992, are currently in place in the U.S. [4], the European Community has already moved toward stronger controls. Restrictions on line harmonics are already in place for household and similar electrical equipment up to 415 V, 16 A [5], [6], and future regulations will apply to equipment with higher ratings [7]. These developments have

Manuscript received November 10, 1997; revised March 3, 1999. Abstract published on the Internet March 1, 1999. This work was supported in part by the Bose Foundation and in part by the Office of Naval Research under Grant N00014-96-1-0524.

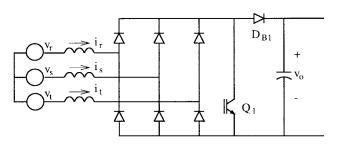

Fig. 1. The three-phase single-switch boost rectifier.

lead to an increased interest in switched-mode rectifiers which draw quasi-sinusoidal input current at high power factor and produce a controlled output voltage.

The full-bridge converter is often used for switched-mode rectification. However, this solution requires a high number of active switches (and attendant ancillary circuitry), and is relatively complex to control. Another approach is to utilize a single-phase switched-mode rectifier for each phase of the three-phase input, although this solution retains much of the complexity of the full-bridge converter. A desire to attain the performance advantages of these rectifiers without the high level of complexity has led to the development of the three-phase single-switch boost rectifier of Fig. 1. This converter topology, introduced in [8], has undergone rapid development in recent years [9]–[18].

The operating principle of this discontinuous-mode converter is as follows. The switch  $Q_1$  is turned on at the beginning of each (fixed-length) switching period and held on for a specified duty cycle d. During this on period, the diode-bridge inputs are shorted together through the diodes and switch  $Q_1$ . Neglecting the effects of the input filter, the inductor currents  $i_r$ ,  $i_s$ , and  $i_t$  rise from zero by an amount proportional to their respective phase voltages. When  $Q_1$  is turned off, the inductor currents return back to zero through diode  $D_{B1}$  and the output capacitor. Thus, the average current delivered from each phase is approximately proportional to the phase voltage, yielding fundamentally resistive behavior. The average total current delivered to the output is controlled by varying the duty cycle of switch  $Q_1$ , while the output voltage  $v_o$  is controllable to voltages above the peak line-to-line mains voltage.

With its supporting input filter, this topology provides high power factor input current waveforms using a single groundreferenced active switch and a very simple control strategy. The discontinuous-mode operation minimizes the energy storage requirements of the input inductors and provides soft turn-off of the diodes. However, it also subjects the devices to relatively high peak current stresses. Furthermore, the converter requires a relatively large input filter to attenuate the input current switching harmonics to acceptable levels (to meet conducted EMI requirements, for example). The size of the input filter is perhaps the single largest drawback of the approach.

Consider the benefits of paralleling cells constructed using the single-switch rectifier topology. The single-switch rectifier has many of the desired characteristics for a utility-interface converter, except for its high level of unfiltered input ripple current harmonics. *Interleaving* of paralleled converter cells, in which the individual cells are switched out of phase, allows a high degree of harmonic cancellation between the cell currents [19]–[23]. This results in greatly reduced aggregate input and output ripple, along with a commensurate reduction in filtering requirements. Interleaving of paralleled singleswitch boost rectifiers has been previously demonstrated to be effective for reducing the high input current ripple associated with this topology [17], [18]. By using a cellular conversion approach (with distributed control), and applying the concept of interleaving, the topology of Fig. 1 can be applied to create a simple, high power factor utility interface with minimal input filtering.

Other advantages of cellular architectures also apply to this application. For example, utility interface converters often need to be constructed in a variety of ratings. By applying a cellular architecture, it is possible to construct a family of systems with a range of ratings using a single cell design. The power rating of a specific system is determined by the number of cells used. Unlike a single large converter, the individual cells can be constructed using single-die devices in inexpensive packages and manufactured using an automated assembly process. The coupling of these facts may lead to a significant cost advantage over a conventionally designed system. Furthermore, because a cellular system can be designed to operate after individual cell failures, significant improvements in reliability and availability may be obtained. Thus, there are several important ancillary advantages to employing a cellular architecture in rectifier applications.

#### **III. INTERLEAVING BENEFITS**

One of the primary benefits of using the three-phase singleswitch boost rectifier in a cellular architecture is the ability to use interleaving to cancel the large input (switching) current ripple drawn by the topology. This is an important benefit, since the input filters required for meeting EMI specifications can be quite large for this converter topology (possibly even larger than the converter itself), due to the fact that it operates in discontinuous conduction mode. This section investigates the amount of ripple reduction which can be expected through interleaving and assesses its likely impact on system design.

One important characteristic of this rectifier is that the switching ripple frequency content includes components not only at the switching frequency and its harmonics, but at the sum and difference frequencies of the line and switching frequencies and their harmonics. Practically speaking, this means that the switching ripple energy is concentrated in bands, which we term switching harmonic *groups*, centered around multiples of the switching frequency.

Regulatory limitations on input current spectral content (such as those set by agencies like the FCC and VDE) tend to be flat over an extremely wide frequency range and are not indexed to equipment power level (see [24], for example). Interleaving N converter cells has two beneficial effects in meeting such EMI limits. First, it tends to attenuate (by cancellation) the first N ripple harmonic groups in the

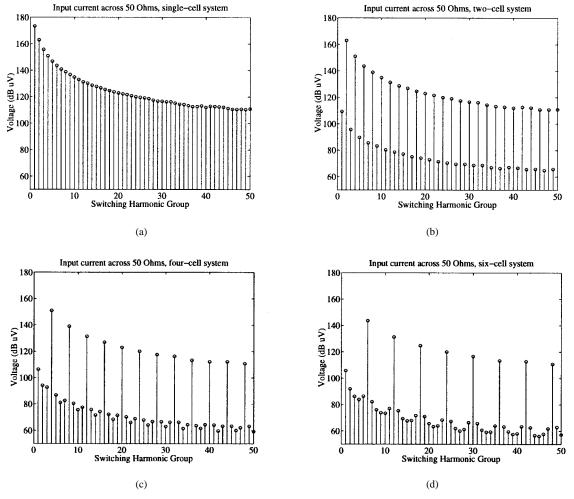

Fig. 2. Worst case input current ripple spectral components for example three-kilowatt rectifier systems. (a) Single-cell system. (b) Two-cell system. (c) Four-cell system. (d) Six-cell system.

spectrum (which are the hardest to attenuate by filtering), as well as harmonic groups at higher frequencies. Second, it reduces the net ripple amplitude by a factor N or more, thus reducing the peak ripple for which the EMI filter has to be designed.

To gain a quantitative understanding of these benefits, consider the comparison of a single large converter with equivalent interleaved converter systems having two, four, and six cells. For our purposes, an "equivalent" system has the same total magnetic energy storage, cell switching frequency, and output power as a single large converter. We consider the example of a 3-kW converter ( $L = 6.7 \mu$ H,  $f_{sw} = 150$  kHz) which generates a 410-V output from a 208-V (line-to-line, rms) input. At each frequency, we compute the worst ripple component that occurs within each switching harmonic group across the load range of the converter and across a +10% to -15% variation in input voltage. Fig. 2(a) shows these worst case spectral components for the single large converter, while Fig. 2(b)–(d) shows the results for equivalent interleaved converter systems with two, four, and six cells.

In the single-cell system, the worst case harmonic component to filter is 173 dB· $\mu$ V at 150 kHz. For the two-cell case, this worst case first harmonic group component is reduced by some 65 dB, leaving the second harmonic-group component as the worst to be filtered (163 dB· $\mu$ V at 300 kHz). The reduction in amplitude and increase in frequency of the worst case component considerably eases the requirements on the EMI filter. With four and six cells, the first major peaks are 151 dB· $\mu$ V at 600 kHz and 143 dB· $\mu$ V at 900 kHz, respectively. (Because higher frequencies are much easier to filter, the first switching harmonic group component may, in fact, *still* be the hardest to filter for these highly interleaved cases.) What is clear from these results is that the amount of EMI filtration required to meet a flat EMI standard is reduced considerably when several cells are interleaved and is significant even for a modest degree of interleaving.

## IV. PROTOTYPE SYSTEM DESIGN

This section describes the design of a six-cell 6-kW prototype system which rectifies the three-phase 208-V mains to a 410-V dc output at high power factor. The input supply voltage is assumed to stay within tolerances of +10% and -15%, while the output voltage is regulated to within  $\pm 3\%$ of nominal. The system implements both distributed load sharing (via the UC3907 load-sharing control method [25]) and distributed interleaving (via the method developed in [26] and

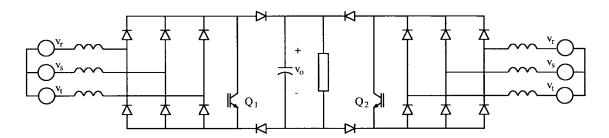

Fig. 3. Structure of a single cell composed of two interleaved single-switch converters.

[27]), eliminating the need for any centralized control. To the authors' knowledge, this is the first system developed in which control of both ripple cancellation and load sharing are entirely distributed. The system is "hot-swap" capable, meaning that individual cells can be removed and inserted (for repair, etc.) while the system is running under load. Furthermore, the system is designed to allow alternative control methods to be easily implemented through the use of "piggyback" control boards. Here, we describe the system architecture, the cell power stage design, and the fusing and protection methods; additional information about the design, layout, and control of the system can be found in [28].

## A. System Architecture

The prototype system has six cells, each of which has a nominal output rating of 1 kW, and is designed to handle a continuous output power of 110% of nominal. The prototype system fits in a standard 19-in rack assembly. Each cell fits in a 6U (10.5 in) high, 14T (2.8 in) wide module, and connects into the backplane via a DIN41612MH connector which is indexed to connect the system ground first upon cell insertion. The power portion of the backplane comprises a low-inductance three-phase input bus and a low-inductance output/ground bus, both of which are wired to an external connector. The connections are such that all of the cells are connected to the low-inductance buses through similar impedances. The control portion of the backplane comprises twisted-pair (signal and ground) interconnections among the cells for "single-wire" communication of current-sharing and ripple-cancellation information.

### B. Cell Power Stage Design

Each cell is constructed on a single printed circuit board as two interleaved single-switch boost rectifiers (which we term *half*-cells) driven from a common control circuit, as illustrated in Fig. 3. This affords some efficiency in the use of control and sensing circuitry and reduces the ripple generated by an individual cell. A photograph of a completed cell is shown in Fig. 4. Note the additional diodes used in the output current return paths of the half-cells, as shown in Fig. 3. (The boost diodes and active switch of one of the half-cells are visible in Fig. 4, mounted to a heat sink behind the control circuitry.) As described in [17] and [18], in order to parallel single-switch rectifiers, each rectifier must have an additional boost diode in its return path. The diode is needed to prevent

Fig. 4. A photograph of a prototype converter cell.

cross conduction among different half-cells; without it, current flowing from the positive phase and through the transistor of one half-cell can return through the negative phases of a different half-cell. Incorporating the additional diode in each half-cell ensures that this cannot happen and makes the halfcells operate independently. In addition to causing a slight decrease in efficiency, the additional diode prevents the active switches from being referenced to ground. As a result, they have to be driven through floating gate drive circuits. However, these disadvantages are heavily outweighed by the tremendous performance increases that can be gained through interleaving.

Design of the cell power stage was centered on the task of selecting the cell inductances and switching frequency such that the cell would meet its rated output power over the specified input voltage range with each half-cell operating in discontinuous conduction mode. This had to be accomplished while meeting the conflicting goals of minimizing component size and cost and minimizing the losses and temperature rises. For a candidate switching frequency, the method of [11] was used to select a boost inductor value, expected semiconductor losses were computed, and candidate inductor designs were identified and their expected losses computed. This process was repeated across a wide range of switching frequencies, yielding a set of candidate designs from which the final design was selected.

From the candidate designs, a switching frequency of 150 kHz and line inductances of 40.4  $\mu$ H were selected for each half-cell. The inductors were constructed using 11 turns of 12-gauge wire on an RM12PA315 core. This core is one size larger than necessary, to provide flexibility for future

uses. IRF840G MOSFET's were used for the main boost switches, and HFA08TB60 ultrafast recovery rectifiers were used for the boost diodes. These were attached to PC-board mountable extruded heat sinks; sufficient cooling was obtained using natural convection, due to the distributed nature of heat generation in the cellular system. MUR160 ultrafast recovery diodes were used for the input bridges. The use of extremely fast diodes for the input bridges was found to be necessary to achieve proper operation at the selected switching frequency. Because the input is three-phase, there is little low-frequency ripple in the output voltage. Hence, only a single 10- $\mu$ F film capacitor was used at the output of each cell.

#### C. Fusing and Protection

Each cell is provided with high-speed (semiconductor) fuses at the input and a slower fuse at the output. Inrush current limiters are placed in series with the boost inductors to soften the startup transient, and the UC3825 PWM controller provides both soft-start and current-limit protection functions. The MOSFET switches have *RCD* snubbers which clamp their drain voltages to a value slightly higher than the output voltage, and a metal oxide varistor (MOV) at the output of each cell provides absolute fault-condition voltage clamping protection. These measures were sufficient to provide for a stable, well-controlled startup (even during hot-swap conditions) and to protect the cells during fault conditions.

#### V. CONTROL DESIGN

Here, we discuss the control design for the cellular rectifier system. The control of the rectifier system is entirely distributed. Each cell has its own output voltage control loop, as well as an outer loop which attempts to balance current with the other cells. Each cell also has its own interleaving controller which adjusts the switching frequency and phase to achieve ripple cancellation with other cells. We will present details about the output voltage control design, the currentsharing control design, and the ripple cancellation control design.

## A. Output Voltage Control

In the baseline configuration of the system, the individual cells employ duty-ratio control of the output voltage. Due to the discontinuous-conduction-mode operation of the half-cells, controlling duty ratio is equivalent to controlling the local average cell output current. Consider a point  $\omega t = \varphi$  in the line cycle where  $\varphi \in [0, \pi/6]$ , and  $\varphi = \pi/12$  is the peak of a line-to-line input voltage. The local average output current at this point is a function of duty ratio and can be shown to be [9]

$$\overline{i}_{out} = \frac{2V_oT}{3L} \cdot \left[\frac{3d^2}{8M^2} \\ \cdot \frac{1 - M^{-1}\cos(\varphi)\cos(2\varphi + \frac{\pi}{6})}{\left(1 + \sqrt{3}M^{-1}\sin(\varphi - \frac{\pi}{6})\right)\left(1 - M^{-1}\cos(\varphi - \frac{\pi}{6})\right)}\right]$$

(1)

where  $V_o$  is the output voltage, T is the switching period, and M is the boost ratio. Using (1), we can make an injected current model for each half-cell

$$i_{\rm out} = K_f d^2 \tag{2}$$

where  $K_f$  varies from 13.75 to 55.0 over the line cycle for the parameters of the prototype system. Considering a proportional controller

$$d = K_p[v_{\rm ref} - v_o] \tag{3}$$

we find an output current characteristic of

$$i_{\rm out} = K_f K_p^2 [V_{\rm ref} - v_o]^2.$$

(4)

The half-cell thus has a (nonlinear) resistive output characteristic, where the output resistance is load-varying and also varies with position in the input line cycle; the output resistance of a full cell is precisely half that of a half-cell. It is easily shown that the incremental output resistance of each half-cell about an operating point is

$$r_{\rm out} = \frac{1}{2K_p\sqrt{K_f I_{\rm out}}}\tag{5}$$

which decreases with load current and is only mildly affected by the position in the line cycle.

The paralleled cells thus exhibit a nonlinear output resistance in parallel with the aggregate output filter capacitance. For a resistive or current-source load, this yields first-order output control dynamics which are stable and well damped [29]. (Essentially, the load impedance appears in parallel with the filter capacitance and cell output resistances, forming a stable *RC* circuit.) Stable output control dynamics also result for constant-power loads. To understand this, recall that a constant-power load of the form

$$i_L = \frac{P_L}{v_o} \tag{6}$$

yields a negative incremental load resistance of

$$r_L = -\frac{P_L}{I_L^2}.$$

(7)

This negative incremental damping tends to have a destabilizing effect and requires great care. In the prototype system, however, the magnitude of the incremental load resistance is much larger than the magnitude of the incremental cell output resistances for any constant-power operating condition within the load range of the system. As a result, the parallel combination of the load resistance and the cell output resistances forms a positive equivalent resistance, and the output control dynamics remain stable and overdamped. The resistive output characteristic which results from the duty-ratio control law (3) thus yields well-behaved output voltage control dynamics for resistive, current-source, and constant-power loads.

For the prototype system, a proportional control gain  $K_p = 0.028 \text{ V}^{-1}$  was selected. This value yields load regulation of less than 5% over the load range and, with a 10- $\mu$ F output capacitor per cell, yields an output voltage control bandwidth that exceeds the 360-Hz input voltage ripple frequency. Furthermore, because the output voltage is controlled with high

bandwidth, the input line current harmonics are reduced as compared to low-bandwidth control [9].

#### B. Current-Sharing Control

In its baseline configuration, the prototype system uses the UC3907 single-wire current-sharing control method [25]. This method operates as follows. To achieve current sharing with the other cells, each cell shifts its own voltage reference via integral control, based on the difference between its own output current and the maximum output current of all the cells minus a small offset. Thus,

$$\frac{dv_{r,j}}{dt} = \begin{cases} K_j[i_{\max} - \Delta I - i_j], & \text{for } v_{r,j,\text{base}} < v_{r,j} < v_{r,j,\max} \\ 0, & \text{otherwise} \end{cases} \tag{8}$$

where  $K_j$  and  $i_j$  are the (integral) control gain and output current of the *j*th cell,  $i_{\text{max}}$  is the maximum output current of all of the cells, and  $\Delta I$  is a small offset. The *j*th reference is adjustable over a small range from a base value  $v_{r,j,\text{base}}$  to a maximum value  $v_{r,j,\text{max}}$  and is prevented from going outside of this range by clamping of the reference at the boundaries. The offset  $\Delta I$  ensures that the highest current cell (which we term the *master* cell) will carry slightly more current than the other cells under static conditions, thus preventing the maximum current signal from chattering among different cell currents. The offset also guarantees that the voltage reference of the master cell will always be driven toward its base value.

Here, we show that the resistive output impedance characteristic of the cells leads to current-sharing dynamics which are stable and overdamped, independent of the number of cells which are operated in parallel. (A more detailed analysis of the UC3907 current-sharing scheme for this case can be found in [29].) We begin by making the simplifying assumption that all of the cells have identical output impedance characteristics, sensor gains, etc., and only differ in their voltage references and current-sharing control gains. Together with the resistive output characteristic of the cells, this condition ensures that a cell with a higher voltage reference will always carry more current than a cell with a lower reference voltage. Because the offset  $\Delta I$  always drives the highest current cell's reference voltage toward its base value, within a short time after startup the cell with the highest base reference will become the master and will remain as the master thereafter. Once this occurs, the other cells will adjust their reference voltages via (8) in a monotonic manner until steady state is reached. The simplicity of this behavior is due to the resistive output impedance characteristic of the cells; behavior of this currentsharing scheme can be substantially more complex under other conditions.

#### C. Ripple Cancellation Control

The prototype system employs both passive and active (interleaving) ripple cancellation. Distributed interleaving is implemented among two groups of (up to) three cells, while the two *groups* of three cells cancel ripple passively, as described

CLOCK GENERATOR Cell 1 Cell 2 Cell N Cell N

Fig. 5. The distributed interleaving approach.

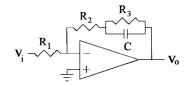

Fig. 6. Loop filter structure for the prototype system.  $C = 0.68 \ \mu$ F,  $R_1 = 90.9 \ k\Omega$ ,  $R_2 = 10 \ k\Omega$ , and  $R_3 = 10 \ M\Omega$ .

in [27]. Thus, within each group, either two, four, or six halfcells are interleaved depending on the number of operational cells within the group. In the distributed interleaving approach, each cell has its own clock generator. All the clock generators within a group are connected via a single-wire interleaving bus (Fig. 5), over which the clock generators share information about their frequencies and phases. Because shared information is only used to adjust the clock frequencies and phases, failures affecting the interleaving bus may shut down the interleaving function, but do not cause the whole system to fail. Furthermore, the approach automatically accommodates varying numbers of cells within a group; proper clock phasing for ripple cancellation is always maintained (180° for two cells,  $120^{\circ}$  for three). This leads to an active ripple cancellation system which is simple, effective, and robust to subsystem failures.

The clock generator structure introduced in [26] and [27] was used to implement the distributed interleaving system. In this implementation, each clock generator injects its own clock onto the interleaving bus and uses a special phase-locked loop to lock out of phase with the other clock signals on the bus. The clock generator design is similar to the system developed in [26] and [27], with slightly different parameters. The clock generators implemented here employ a phase detector gain,  $K_d$ , of 7.95 and a VCO gain,  $K_o$ , of 6090 rad/(V·s). Both the base operation frequency and the phase detector gain can be adjusted via potentiometer settings. The loop filter of Fig. 6 is employed in the prototype system, yielding clock-phase control dynamics which are stable and well damped for up to three cells in a group.

#### VI. EXPERIMENTAL RESULTS

This section presents some experimental results from the prototype converter system. The prototype converter system was run both from the Cambridge utility through an isolation transformer and from a Hewlett-Packard 6834B three-phase ac source.

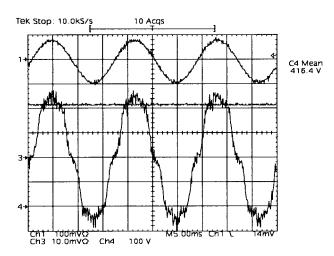

Fig. 7. Circuit waveforms for three cells operating at 97% of full load  $(R_L = 60.2 \ \Omega)$  from a 6834B ac source (60 Hz, 208 V). Channel 1 is the line voltage (200 V/div), channel 3 is the line current (5 A/div), and channel 4 is the output voltage (100 V/div). Note that the observed switching ripple is undersampled by the oscilloscope.

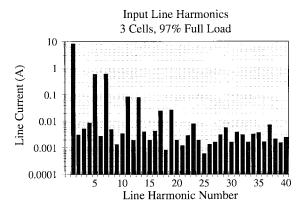

Fig. 8. Input line harmonic data for three cells operating at 97% of full load  $(R_L = 60.2 \ \Omega)$  from a 6834B ac source (60 Hz, 208 V).

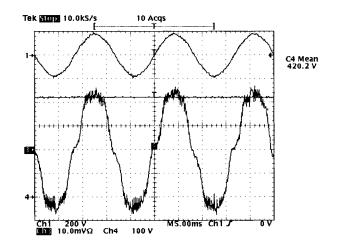

The prototype system operated as designed over the entire load range. Fig. 7 shows operation of the prototype system at 97% of full load (for three cells). As can be seen, the line current waveforms are quasi-sinusoidal, with the expected waveform shape (see [9]). As illustrated in Fig. 8, the measured line harmonic content matches the theoretical predictions of [9] very closely, with the fifth and seventh harmonics contributing the majority of distortion. The power factor for this load condition is 0.994, with 10.3% total harmonic distortion (based on 40 harmonics), both of which match theoretical predictions. Similar results are obtained for operation with six cells, as can be seen in Fig. 9.

While the harmonic content drawn by the system is as designed and is sufficiently low to meet European harmonic limits [5], [6] over much of the load range, the European limits are exceeded when operating with six cells at heavy load. If it is desired to meet the European limits at this power level using the single-switch boost rectifier cell topology, two courses of action are possible. The first is to operate the system at a higher boost ratio (higher output voltage or lower input voltage), although this is often not acceptable. A more tenable

Fig. 9. Circuit waveforms for six cells operating at 97% of full load  $(R_L = 30 \ \Omega)$  from the Cambridge utility through an isolation transformer. Channel 1 is the line voltage (200 V/div), channel 3 is the line current (10 A/div), and channel 4 is the output voltage (100 V/div). Note that the observed switching ripple is undersampled by the oscilloscope.

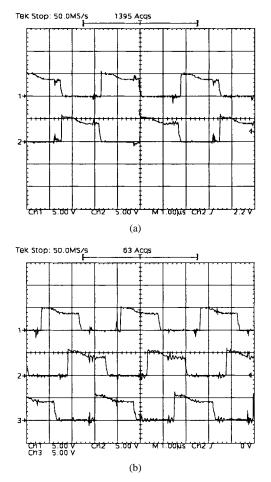

Fig. 10. Clock waveforms for (a) two and (b) three cells. The system was operating at 70% of rated load in both cases.

approach is to modify the duty ratio control of the cells in order to reduce the line harmonic content, such as described in [16].

As can be seen from the small level of ripple in the line current of Figs. 7 and 9, the distributed interleaving greatly

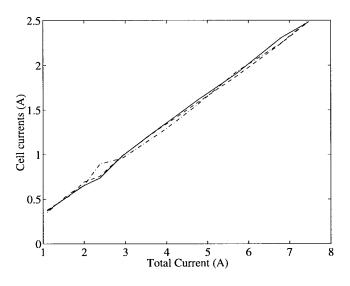

Fig. 11. Current-sharing data for three cells.

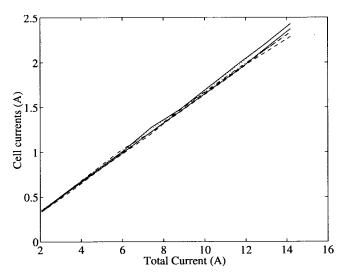

Fig. 12. Current-sharing data for six cells.

reduced the input switching ripple as compared to the noninterleaved case. The distributed interleaving circuitry functioned as expected over the load range for the cases of both two- and three-cell groups, and the two interleaving groups operated independently (as desired) for up to the full complement of six cells. Fig. 10 shows the clocks of the individual cells with the system at 70% of full load for both the two- and three-cell cases. As can be seen, the distributed interleaving circuitry properly phased the individual switching waveforms in order to cancel the switching ripple in both cases.

The load-sharing and output voltage control behavior of the system also met performance expectations. Fig. 11 shows the current-sharing characteristic for three cells over the load range, while Fig. 12 shows the current-sharing characteristic for six cells. Acceptable current sharing is achieved over the whole load range, with current sharing within a few percent achieved over most of the range. The output voltage was regulated to within specifications over the whole load range, and the transient response was stable and over damped (as expected) for even large load steps.

## VII. CONCLUSION

The use of cellular converter architectures for the construction of switched-mode rectifier systems has several potential advantages over conventional approaches, including improvements in performance, reliability, and cost. To realize these advantages, however, it is necessary to develop the appropriate design and control approaches and demonstrate them experimentally. This paper has presented the design and experimental evaluation of a prototype cellular rectifier system which uses entirely distributed control. The performance increases that can be obtained through interleaving of the cells have been quantified. The design of the cellular rectifier system has been addressed, including the system architecture, the power stage design, and the fusing and protection methods. The control design for the cellular converter has also been described, including the methods used to control the output voltage while regulating current-sharing among cells, and the methods used to obtain ripple cancellation among the cells. Finally, an experimental evaluation of the prototype system has been performed.

It may be concluded from the experimental results that the prototype system successfully demonstrates the technical feasibility of the cellular design approach for this application. Controlled, high-power-factor rectification is achieved along with excellent output voltage and load-sharing regulation using entirely distributed control. The system also achieves a high degree of input switching ripple cancellation as compared to a single large converter implementation, without requiring a centralized controller. This advantage alone merits the further development of the approach.

#### ACKNOWLEDGMENT

The authors would like to express their appreciation for the generous equipment grants from the Tektronix and Intel Corporations, which facilitated this research.

#### REFERENCES

- J. G. Kassakian, "High frequency switching and distributed conversion in power electronic systems," in *Proc. 6th Conf. Power Electronics and Motion Control (PEMC'90)*, Budapest, Hungary, 1990.

- [2] J. G. Kassakian and D. J. Perreault, "An assessment of cellular architectures for large converter systems," in *Proc. 1st Int. Conf. Power Electronics and Motion Control*, Beijing, China, 1994, pp. 70–79.

- [3] T. Kohama, T. Ninomiya, and M. Shoyama, "Characteristics of a parallel-module high power-factor AC-to-DC converter system with current-balancing controllers," in *Proc. IEEE Int. Telecommunications Energy Conf.*, 1995, pp. 791–795.

- [4] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, IEEE Standard 519-1992.

- [5] Electromagnetic Compatability (EMC)—Part 3: Limits—Section 2: Limits for Harmonic Current Emissions, IEC Standard IEC1000-3-2.

- [6] Disturbances in Supply Systems Caused by Household Appliances and Similar Electrical Equipment—Part 2: Harmonics, European Standard EN 60555-2.

- [7] T. Key, "Standards for harmonic control—Protecting the electric power supply," *IEEE Standards Bearer*, Apr. 1994.

- [8] A. R. Prasad, P. D. Ziogas, and S. Manias, "An active power factor correction technique for three-phase diode rectifiers," *IEEE Trans. Power Electron.*, vol. 6, pp. 83–92, Jan. 1991.

- [9] J. W. Kolar, H. Ertl, and F. Zach, "Space vector-based analytical analysis of the input current distortion of a three-phase discontinuous-mode boost rectifier system," in *Proc. IEEE PESC'93*, Seattle, WA, 1993, pp. 696–703.

- [10] D. S. L. Simonetti, J. Sebastian, and J. Uceda, "Single-switch threephase power factor preregulator under variable switching frequency and discontinuous input current," in *Proc. IEEE PESC'93*, Seattle, WA, 1993, pp. 657–662.

- [11] J. W. Kolar, H. Ertl, and F. Zach, "A comprehensive design approach for a three-phase high-frequency single-switch discontinuous-mode boost power factor corrector based on analytically derived normalized converter component ratings," *IEEE Trans. Ind. Applicat.*, vol. 31, pp. 569–582, May/June 1995.

- [12] E. H. Ismail and R. Erickson, "Single-switch 3φ PWM low harmonic rectifiers," *IEEE Trans. Power Electron.*, vol. 11, pp. 338–346, Mar. 1996.

- [13] K. Chen, A. Elasser, and D. A. Torrey, "A soft switching active snubber optimized for IGBT's in single switch unity power factor three-phase diode rectifiers," in *Proc. IEEE APEC'94*, 1994, pp. 280–286.

[14] S. Gatarić, D. Boroyevich, and F. C. Lee, "Soft-switched single-

- [14] S. Gatarić, D. Boroyevich, and F. C. Lee, "Soft-switched singleswitch three-phase rectifier with power factor correction," in *Proc. IEEE APEC'94*, 1994, pp. 738–744.

- [15] R. L. Lin and F. C. Lee, "Novel zero-current-switching-zero-voltageswitching converters," in *Proc. IEEE PESC'96*, Baveno, Italy, Sept. 1996, pp. 438–442.

- [16] Q. Huang and F. C. Lee, "Harmonic reduction in a single-switch, threephase boost rectifier with high order harmonic injected PWM," in *Proc. IEEE PESC'96*, Baveno, Italy, Sept. 1996, pp. 1266–1271.

- [17] V. Chunkag and F. V. P. Robinson, "Interleaved switching topology for three-phase power-factor correction," in *Proc. 5th Int. Conf. Power Electronics and Variable Speed Drives*, London, U.K., Oct. 1994, pp. 280–285.

- [18] F. V. P. Robinson and V. Chunkag, "Parallel connection of singleswitch three-phase power-factor correction converters for interleaved switching," *Proc. Inst. Elect. Eng.—Elect. Power Applicat.*, vol. 144, no. 6, pp. 423–433, Nov. 1997.

- [19] B. A. Miwa, D. M. Otten, and M. F. Schlecht, "High efficiency power factor correction using interleaving techniques," in *Proc. IEEE APEC'92*, Boston, MA, 1992, pp. 557–568.

- [20] B. A. Miwa, "Interleaved conversion techniques for high density power supplies," Ph.D. dissertation, Dep. Elect. Eng. Comput. Sci., Massachusetts Inst. Technol., Cambridge, June 1992.

- [21] M. Albach and D. Dambois, "Optimized operation mode for 3 kW offline preconditioner circuits," in *Proc. 1991 European Power Electronics Conf.*, Florence, Italy, 1991, pp. 3-134–3-139.

- [22] C. Chang, "Current ripple bounds in interleaved DC-DC power converters," in *Proc. 1995 Int. Conf. Power Electronics and Drive Systems*, Singapore, 1995, pp. 738–743.

- [23] C. Chang and M. Knights, "Interleaving technique in distributed power conversion systems," *IEEE Trans. Circuits Syst. I*, vol. 42, pp. 245–251, May 1995.

- [24] Federal Communications Commission, Code of Federal Regulations, Title 47, Part 15.

- [25] M. Jordan, "UC3907 load share IC simplifies parallel power supply design," Unitrode Corp., Merrimack, NH, Application Note U-129.

[26] D. J. Perreault and J. G. Kassakian, "Distributed interleaving of power

- [26] D. J. Perreault and J. G. Kassakian, "Distributed interleaving of power converters," in *Proc. 7th Int. Power Electronics and Motion Control Conf.*, Budapest, Hungary, Sept. 1996, pp. 2/149–2/153.

- [27] D. J. Perreault and J. G. Kassakain, "Distributed interleaving of paralleled power converters," *IEEE Trans. Circuits Syst. I*, vol. 44, pp. 728–734, Aug. 1997.

- [28] D. J. Perreault, "Design and evaluation of cellular power converter architectures," Ph.D. dissertation, Dep. Elect. Eng. Comput. Sci., Massachusetts Inst. Technol., Cambridge, June 1997.

- [29] D. J. Perreault, J. G. Kassakian, and G. C. Verghese, "Stability analysis of nonlinear current-sharing techniques," in *Proc. IEEE PESC*'97, St. Louis, MO, June 1997, pp. 665–671.

**David J. Perreault** (M'98) was born in North Providence, RI, in 1967. He received the B.S. degree from Boston University, Boston, MA, in 1989 and the S.M. and Ph.D. degrees from Massachusetts Institute of Technology, Cambridge, in 1991 and 1997, respectively, all in electrical engineering.

He is currently a Postdoctoral Researcher in the Laboratory for Electromagnetic and Electronic Systems, Massachusetts Institute of Technology, where his work includes the investigation of new methods for the design and control of power electronic

systems.

Dr. Perreault is a member of Tau Beta Pi, Sigma Xi, and the National Society of Professional Engineers.

John G. Kassakian (S'65–M'73–SM'80–F'89) received the Sc.D. degree from Massachusetts Institute of Technology, Cambridge, in 1973.

He is a Professor of Electrical Engineering and Director of the Massachusetts Institute of Technology Laboratory for Electromagnetic and Electronic Systems, Massachusetts Institute of Technology. His fields of expertise are power electronics and automotive electrical systems, and he serves as a consultant to government and industry. He has published extensively in the area of power electronics and is a

coauthor of *Principles of Power Electronics* (Reading, MA: Addison-Wesley, 1991). He serves as the U.S. representative to the European Power Electronics Society.

Dr. Kassakian was the Founding President of the IEEE Power Electronics Society. He is the recipient of the IEEE Centennial Medal, the IEEE William E. Newell Award, the IEEE Distinguished Lectureship Award, and the Distinguished Service Award. In 1993, he was elected to the National Academy of Engineering.