#### US011316477B2

# (12) United States Patent

Jurkov et al.

# (10) Patent No.: US 11,316,477 B2

(45) **Date of Patent:**

Apr. 26, 2022

#### (54) GENERATION AND SYNCHRONIZATION OF PULSE-WIDTH MODULATED (PWM) WAVEFORMS FOR RADIO-FREQUENCY (RF) APPLICATIONS

(71) Applicant: Massachusetts Institute of

Technology, Cambridge, MA (US)

(72) Inventors: Alexander Sergeev Jurkov,

Somerville, MA (US); **David J. Perreault**, Cambridge, MA (US)

(73) Assignee: Massachusetts Institute of

Technology, Cambridge, MA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 16/932,327

(22) Filed: Jul. 17, 2020

#### (65) **Prior Publication Data**

US 2020/0350863 A1 Nov. 5, 2020

#### Related U.S. Application Data

(60) Division of application No. 16/126,553, filed on Sep. 10, 2018, now Pat. No. 10,790,784, which is a (Continued)

(51) **Int. Cl.**

*H03F 1/02* (2006.01) *H03F 1/56* (2006.01)

(Continued)

(52) U.S. Cl.

(Continued)

## (58) Field of Classification Search

CPC ....... H03F 1/0205; H03F 3/245; H03F 1/565; H03F 3/2171; H03F 3/193; H03F 3/2176; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,800,167 A 3/1974 Smith 5,195,045 A 3/1993 Keane et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 101297480 A 10/2008 CN 103181086 6/2013 (Continued)

#### OTHER PUBLICATIONS

Response to Office Action for Chinese Patent Application No. 201580069046.1 as filed on Jul. 27, 2020 with English Translation; 14 Pages.

(Continued)

Primary Examiner — Hieu P Nguyen (74) Attorney, Agent, or Firm — Daly, Crowley, Mofford & Durkee LLP

#### (57) ABSTRACT

Described are concepts, systems, circuits and techniques directed toward methods and apparatus for generating one or more pulse width modulated (PWM) waveforms with the ability to dynamically control pulse width and phase with respect to a reference signal.

#### 20 Claims, 38 Drawing Sheets

### Related U.S. Application Data

continuation-in-part of application No. 15/918,410, filed on Mar. 12, 2018, now abandoned, which is a continuation of application No. 14/975,742, filed on Dec. 19, 2015, now Pat. No. 9,923,518, which is a continuation of application No. 14/974,563, filed on Dec. 18, 2015, now Pat. No. 9,755,576.

(60) Provisional application No. 62/094,144, filed on Dec. 19, 2014.

```

(51) Int. Cl.

H03F 3/19

(2006.01)

H03F 3/21

(2006.01)

H03F 3/24

(2006.01)

H03F 3/217

(2006.01)

H03F 3/193

(2006.01)

H03K 7/08

(2006.01)

H03H 7/38

(2006.01)

```

(52) U.S. Cl.

CPC ...... H03F 3/193 (2013.01); H03F 3/21  $(2013.01); \textit{H03F 3/2171} \ (2013.01); \textit{H03F}$ 3/2176 (2013.01); H03F 3/245 (2013.01); H03K 7/08 (2013.01); H03F 3/2178 (2013.01); H03F 2200/301 (2013.01); H03F 2200/387 (2013.01); H03F 2200/391 (2013.01); H03F 2200/451 (2013.01); H03H 7/38 (2013.01)

#### (58) Field of Classification Search

CPC ..... H03F 3/21; H03F 3/19; H03F 1/56; H03F 3/2178; H03F 2200/391; H03F 2200/387; H03F 2200/451; H03F 2200/301; H03K 7/08; H03H 7/38

See application file for complete search history.

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

| 6,239,996 | B1   | 5/2001  | Perreault et al.  |             |

|-----------|------|---------|-------------------|-------------|

| 6,346,797 | B1   | 2/2002  | Perreault et al.  |             |

| 6,456,514 | B1   | 9/2002  | Perreault et al.  |             |

| 6,587,017 | В1   | 7/2003  | Sheng et al.      |             |

| 6,671,195 | B2   | 12/2003 | Perreault et al.  |             |

| 6,887,339 | В1   | 5/2005  | Goodman et al.    |             |

| 6,900,997 | B2   | 5/2005  | Perreault et al.  |             |

| 6,937,115 | B2   | 8/2005  | Perreault et al.  |             |

| 7,242,269 | B2   | 7/2007  | Perreault et al.  |             |

| 7,535,133 | B2   | 5/2009  | Perreault et al.  |             |

| 7,589,605 | B2   | 9/2009  | Perreault et al.  |             |

| 7,825,715 | B1 * | 11/2010 | Greenberg         | H03B 5/1228 |

|           |      |         |                   | 327/337     |

| 7,889,519 | B2   | 2/2011  | Perreault et al.  |             |

| 8,054,892 | B2   | 11/2011 | Aziz et al.       |             |

| 8,174,233 | B2   | 5/2012  | Julstrom et al.   |             |

| 8,212,541 | B2   | 7/2012  | Perreault et al.  |             |

| 8,279,950 | B2   | 10/2012 | Aziz et al.       |             |

| 8,339,174 | B2   | 12/2012 | Yang et al.       |             |

| 8,451,053 | B2   | 5/2013  | Perreault et al.  |             |

| 8,625,654 | B2 * | 1/2014  | Jeong             | H04B 1/7174 |

|           |      |         |                   | 375/130     |

| 8,633,782 | B2   | 1/2014  | Nagarkatti et al. |             |

| 8,643,347 | B2   | 2/2014  | Giuliano et al.   |             |

| 8,670,254 | B2   | 3/2014  | Perreault et al.  |             |

| 8,699,248 | B2   | 4/2014  | Giuliano et al.   |             |

| 8,718,188 | B2   | 5/2014  | Balteanu et al.   |             |

| 8,830,709 |      | 9/2014  | Perreault et al.  |             |

| 8,830,710 | B2   | 9/2014  | Perreault et al.  |             |

| 8,890,618 | B2   | 11/2014 | Pamarti et al.    |             |

| 9,141,832 | B2   | 9/2015  | Perreault et al.  |             |

|           |      |         |                   |             |

| 9,374,020 B2    | 6/2016  | Pereault et al.  |

|-----------------|---------|------------------|

| 9,401,664 B2    | 7/2016  | Perreault et al. |

| 9,407,164 B2    | 8/2016  | Chang et al.     |

| 9,490,752 B2    | 11/2016 | Briffa et al.    |

| 9,537,456 B2    | 1/2017  | Briffa et al.    |

| 9,634,577 B2    | 4/2017  | Perreault et al. |

| 9,660,520 B2    | 5/2017  | Perreault et al. |

| 9,755,576 B2    | 9/2017  | Perreault et al. |

| 9,755,672 B2    | 9/2017  | Perreault et al. |

| 9,762,145 B2    | 9/2017  | Perreault et al. |

| 9,768,731 B2    | 9/2017  | Perreault et al. |

| 9,768,732 B2    | 9/2017  | Briffa et al.    |

| 9,819,272 B2    | 11/2017 | Perreault et al. |

| 9,825,545 B2    | 11/2017 | Chen et al.      |

| 9,853,550 B2    | 12/2017 | Perreault et al. |

| 9,912,303 B2    | 3/2018  | Barton et al.    |

| 9,923,518 B2    | 3/2018  | Perreault et al. |

| 10,038,461 B2   | 7/2018  | Briffa et al.    |

| 10,075,064 B2   | 9/2018  | Perreault et al. |

| 10,536,093 B2   | 1/2020  | Perreault et al. |

| 2005/0286278 A1 | 12/2005 | Perreault et al. |

| 2007/0090874 A1 | 4/2007  | Sorrells et al.  |

| 2008/0218291 A1 | 9/2008  | Zhu et al.       |

| 2012/0056689 A1 | 3/2012  | Spears et al.    |

| 2013/0033118 A1 | 2/2013  | Karalis et al.   |

| 2013/0285741 A1 | 10/2013 | Wright           |

| 2014/0226378 A1 | 8/2014  | Perreault et al. |

| 2014/0266433 A1 | 9/2014  | Nobbe et al.     |

| 2014/0355322 A1 | 12/2014 | Perreault et al. |

| 2015/0023063 A1 | 1/2015  | Perreault et al. |

| 2015/0084701 A1 | 3/2015  | Perreault et al. |

| 2015/0188448 A1 | 7/2015  | Perreault et al. |

| 2016/0173032 A1 | 6/2016  | Kuttner          |

| 2018/0102644 A1 | 4/2018  | Perreault et al. |

| 2019/0006995 A1 | 1/2019  | Jurkov et al.    |

|                 |         |                  |

#### FOREIGN PATENT DOCUMENTS

| CN | 103181086 A       | 6/2013  |

|----|-------------------|---------|

| CN | 103378811 A       | 10/2013 |

| CN | 103444078 A       | 12/2013 |

| EP | 0 786 863 A2      | 1/1997  |

| EP | 0 821 304 B1      | 2/2002  |

| EP | 2 582 039 A2      | 4/2013  |

| JР | Н 104335          | 1/1998  |

| JР | 2002-158556       | 5/2002  |

| JР | 2002-271160       | 9/2002  |

| JР | 2007-501600 A     | 1/2007  |

| JР | 2014-187678       | 10/2014 |

| WO | WO 2004/105208 A1 | 12/2004 |

| WO | WO 2018/005795 A1 | 1/2018  |

#### OTHER PUBLICATIONS

International Preliminary Report on Patentability dated Mar. 25, 2021 for International Application No. PCT/US2019/046595; 6 Pages

European Communication pursuant to Rules 161(2) and 162 EPC dated Apr. 21, 2021 for European Application No. 19859116.6; 3

Chinese Office Action (with English Translation from Espacenet. com) dated Mar. 30, 2021 for Chinese Application No. CN201580069046.1; 71 Pages.

U.S. Appl. No. 13/722,659, filed Dec. 20, 2012, Perreault, et al. U.S. Appl. No. 15/797,491, filed Oct. 30, 2017, Perreault, et al. U.S. Appl. No. 15/918,410, filed Mar. 12, 2018, Perreault, et al.

F. Chan Wai Po, et. al., "A novel method for synthesizing an automatic matching network and its control unit," IEEE Transactions on Circuits and Systems-I, vol. 58, No. 9, pp. 2225-2235, Sep. 2011 (12 pages).

T. Nesimoglu, et. al., "A frequency tunable broadband amplifier utilizing tunable capacitors and inductors," 2013 Conference on Microwave Techniques, pp. 65-68, Apr. 2013 (4 pages).

Y. Sun, J. Moritz, and X. Zhu, "Adaptive impedance matching and antenna tuning for green software-defined and cognitive radio," 2011 IEEE 54th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1-4, Aug. 2011. (4 pages).

#### (56) References Cited

#### OTHER PUBLICATIONS

Y. Lim, et. al., "An adaptive impedance-matching network based on a novel capacitor matrix for wireless power transfer," *IEEE Transactions on Power Electronics*, vol. 29, No. 8, pp. 4403-4413, Aug. 2014. (11 pages).

G. J. J. Winands, et. al., "Matching a pulsed power modulator to a corona plasma reactor," 2007 IEEE International Pulsed Power Conference, pp. 587-590, Jun. 2007. (4 pages).

Nemati, et. al., "Design of Varactor-based tunable matching networks for dynamic load modulation of high power amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, No. 5, pp. 1110-1118, May 2009. (9 pages).

W. C. E. Neo, et. al., "Adaptive multi-band multi-mode power amplifier using integrated Varactor-based tunable matching networks," *IEEE Journal of Solid-State Circuits*, vol. 41, No. 9, pp. 2166-2176, Sep. 2006. (11 pages).

Q. Shen and N. S. Barker, "Distributed MEMS tunable matching network using minimal-contact RF-MEMS varactors," *IEEE Transactions on Microwave Theory and Technology*, vol. 54, No. 6, pp. 2646-2658, Jun. 2006. (13 pages).

A. van Bezooijen, et. al., "A GSM/EDGE/WCDMA adaptive series-LC matching network using RF-MEMS switches," *IEEE Journal of Soli-State Circuits*, vol. 43, No. 10, pp. 2259-2268, Oct. 2008. (10 pages).

C. Sanchez-Perez, et al., "Design and applications of a 300-800 MHz tunable matching network," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 3, No. 4, Dec. 2013 (10 pages).

P. Sjoblom and H. Sjoland, "Measured CMOS switched highquality capacitors in a reconfigurable matching network," *IEEE Transactions on Circuits and Systems II*, vol. 54, No. 10, pp. 858-862, Oct. 2007 (5 pages).

R. Malmqvist, et al., "RF MEMS based impedance matching networks fortunable multi-band microwave low noise amplifiers," in *Proc. 2009 International Semiconductor Conference*, vol. I, pp. 303-306. (4 pages).

J. Mitola, "The software radio architecture," *IEEE Communications Magazine*, vol. 33, No. 5, pp. 26-38, May 1995. (13 pages).

E. Din, et al., "Efficiency enhancement of class-F GaN power amplifiers using load modulation," 2010 German Microwave Conference, pp. 114-117, Mar. 15-17, 2010. (4 pages).

M. Schmidt, et al., "A comparison of tunable ferroelectric II- and T-matching networks," in *Proc. 37th European Microwave Conference*, pp. 98-101, Oct. 9-12, 2007. (4 pages).

W. Gu, and K. Harada, "A new method to regulate resonant converters," *IEEE Transactions on Power Electronics*, vol. 3, No. 4, Oct. 1988 (10 pages).

A. Jurkov, L. Roslaniec, and D. Perreault, "Lossless multiway power combining and outphasing for high-frequency resonant inverters," *IEEE Transactions on Power Electronics*, vol. 29, No. 4, pp. 1894-1908, Apr. 2014. (15 pages).

L. Roslaniec, et al., "Design of single-switch inverters for variable resistance/load modulation operation," *IEEE Transactions on Power Electronics*, accepted for publication (15 pages).

E. Waffenschmidt, "Dynamic Resonant Matching Method for a Wireless Power Transmission Receiver", *IEEE Transactions on Power Electronics*, vol. 30, No. 11, Nov. 2015 (8 pages).

PCT Search Report and Written Opinion of the ISA dated Apr. 21, 2016; for PCT Pat App. No. PCT/US2015/066722; 16 pages.

Office Action dated Feb. 8, 2017 from U.S. Appl. No. 14/974,563; 19 Pages.

Denieport; "Medical Power Generator Using a Voltage Mode Resonant Converter Controlled by a Synchronous Switched Capacitor is MRI Compatible"; 2014 21<sup>st</sup> IEEE International Conference on Electronics, Circuits and Systems (ICECS); Dec. 7-10, 2014; 4 Pages.

Response to Office Action dated Feb. 8, 2017 from U.S. Appl. No. 14/974,563, filed May 8, 2017; 8 Pages.

PCT International Preliminary Report on Patentability dated Jun. 29, 2017 from International Application No. PCT/US2015/066722; 10 Pages.

Notice of Allowance dated Jul. 17, 2017 from U.S. Appl. No. 14/974,563; 11 Pages.

Office Action dated Oct. 5, 2016 for U.S. Appl. No.  $14/975,742;\,11$  pages.

Response to Office Action dated Oct. 5, 2016 for U.S. Appl. No. 14/975,742, filed Jan. 5, 2017, 14 pages.

Final Office Action dated Mar. 7, 2017 for U.S. Appl. No. 14/975,742; 13 pages.

Response to Final Office Action dated Mar. 7, 2017 for U.S. Appl. No. 14/975,742, filed Jun. 7, 2017, 13 pages.

Notice of Allowance dated Dec. 8, 2017 for U.S. Appl. No. 14/975,742; 8 pages.

International Search Report of the ISA for Int'l. Appl. No. PCT/US2017/040000 dated Nov. 3, 2017; 5 pages.

International Written Opinion of the ISA for Int'l. Appl. No. PCT/US2017/040000 dated Nov. 3, 2017; 6 pages.

Notice of Rejection with English translation dated Aug. 28, 2018 for Japanese Appl. No. 2017-532742; 10 pages.

Response (with English Translation) to Japanese Office Action dated Aug. 24, 2018 for Japanese Application No. 2017-532742; Response filed on Feb. 28, 2019; 20 Pages.

Japanese Office Action dated Jul. 11, 2019 (with English Translation) for Japanese Application No. 2017-532742; 8 pages.

Response to Office Action with English claims filed Oct. 10, 2019 for Japanese Application No. 2017-532742; 13 pages.

International Search Report and Written Opinion of the ISA dated Dec. 27, 2019 for International Application No. PCT/US2019/046595; 13 Pages.

Intention of Grant dated Mar. 2, 2020 for Japanese Application No. 2017-532742; 5 pages.

Chinese Office Action with English Translation dated Mar. 11, 2020 for Chinese Application No. 201580069046.1; 56 Pages.

Restriction Requirement dated Oct. 3, 2019 for U.S. Appl. No. 16/126,553; 5 Pages.

Response to Restriction Requirement dated Oct. 3, 2019 for U.S. Appl. No. 16/126,553, filed Oct. 18, 2019; 1 Page.

Office Action dated Dec. 18, 2019 for U.S. Appl. No. 16/126,553; 21 Pages.

Response to Office Action dated Dec. 18, 2019 for U.S. Appl. No. 16/126,553, filed Mar. 16, 2020; 9 Pages.

Notice of Allowance dated May 4, 2020 for U.S. Appl. No. 16/126,553; 9 Pages.

Office Action dated Aug. 17, 2020 for Chinese Application No. 201580069046.1 with English Translation; 12 Pages.

Chinese Decision of Rejection (with English Translation) dated Nov. 2, 2021 for Chinese Application No. CN201580069046.1; 71 Pages.

\* cited by examiner

FIG. 2

FIG. 4

402

LEFF

406

Q

404

LOS VIL

FIG. 9

LOAD 3 100 SOURCE

FIG. 13 <u>1300</u>

FIG. 14 <u>1400</u>

FIG. 24 <u>2400</u> START OPERATION 2402 OF TMN 112 2404 DETERMINE DESIRED IMPEDANCE TRANSFORMATION OF TMN 112 YES -2406 r 2410 INCREASE CHANGE REACTANCE NO INCREASE REACTANCE SWITCHING PHASE ANGLE VALUE? YES - DECREASE REACTANCE DECREASE 2408 SWITCHING PHASE ANGLE

2800

FIC. 28

F.C. 31

FIG. 38

FIG. 40

FIC. 414

FIG. 43

## GENERATION AND SYNCHRONIZATION OF PULSE-WIDTH MODULATED (PWM) WAVEFORMS FOR RADIO-FREQUENCY (RF) APPLICATIONS

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a divisional of co-pending U.S. application Ser. No. 16/126,553 filed Sep. 10, 2018 which is a 10 continuation-in-part (CIP) of U.S. application Ser. No. 15/918,410 filed Mar. 12, 2018 (now abandoned) which is a continuation of U.S. application Ser. No. 14/975,742 filed on Dec. 19, 2015, now U.S. Pat. No. 9,923,518 B2 which is a continuation of U.S. application Ser. No. 14/974,563, filed 15 on Dec. 18, 2015, now U.S. Pat. No. 9,755,576 which claims the benefit under 35 U.S.C. § 119(e) of U.S. provisional application No. 62/094,144, filed on Dec. 19, 2014. Application Ser. No. 14/975,742 filed on Dec. 19, 2015, now U.S. Pat. No. 9,923,518 B2 also claims the benefit under 35 20 U.S.C. § 119(e) of U.S. provisional application No. 62/094, 144, filed on Dec. 19, 2014. Each of the above applications are hereby incorporated herein by reference in their entireties.

#### **BACKGROUND**

As is known in the art, impedance matching networks are commonly used for maximizing power transfer within many radio frequency (RF) and microwave systems. For example, 30 in RF transmitters, impedance matching networks might be used to provide an impedance match from an output impedance of an RF power amplifier (PA) to an impedance of an RF load (e.g., an antenna). Such impedance matching increases the transmitted power, reduces power loss and 35 reduces or eliminates the need for additional circuit elements (e.g., isolators, etc.).

One class of impedance matching networks is referred to as tunable impedance matching networks (TMNs), sometimes called automatic antenna tuning units. Conventional 40 TMNs might be implemented as single-element or lumped-element reactive networks where at least one of the reactive elements are variable (e.g., tunable) components such that the impedance of the variable components at a particular frequency, or over a range of frequencies, can be modified. 45 The reactive elements within a TMN might be arranged in circuit topologies such as a ladder-network, an L-network, a T-network, or a Pi-network.

Conventional TMNs can be classified as either analog (continuously adjustable) or digital (adjustable among a set 50 of discrete values). Analog TMNs utilize variable reactance elements having reactance values (at some frequency or over a range of frequencies) that can be tuned in a continuous manner by adjusting bias conditions. Digital TMNs implement the variable reactive elements as digitally switched 55 arrays of static reactance elements. This approach allows adjustment of the impedance of the reactance values in finite and discrete steps.

Analog TMNs are often implemented using varactor diodes (or varactor diode circuits) or micro-electromechanical systems (MEMS) varactors. Although analog TMNs allow fast and accurate impedance matching over a wide range of impedances, relatively high bias voltages are required to operate at high power levels.

Digital TMNs are often implemented using CMOS 65 switches, MEMS switches, PIN diodes or discrete power transistors. Although MEMS switches have low on-state

2

resistance and can operate up to tens of GHz with low power consumption, MEMS switches require large control voltages. PIN diode and CMOS switch-based digital TMNs exhibit low-to-moderate on-state resistance and, thus, can handle high power levels at the expense of some resistive power loss. PIN diode and CMOS switch-based digital TMNs are favorable for on-die integration, for example for Software Defined Radio (SDR) integrated circuits (ICs) and other on-chip TMNs. Digital TMNs, however, exhibit limited tuning resolution, and hence, limited accuracy with which impedance matching can be achieved. In some high power applications where accurate impedance matching is required over a very wide impedance range, such as RF plasma drivers, the use of digital TMNs can be impractical due to the large number of digital switches needed to achieve the required fine-tuning resolution.

#### **SUMMARY**

This Summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This Summary is not intended to identify key or essential features or combinations of the claimed subject matter, nor is it intended to be used to limit the scope of the claimed subject matter.

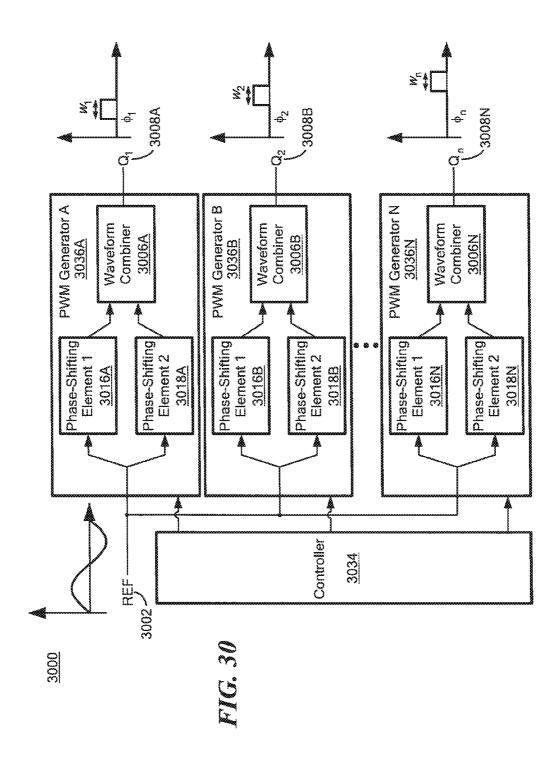

In general overview, the concepts, systems and techniques described herein are directed toward methods and apparatus for generating one or more pulse width modulated (PWM) waveforms (signals) with the ability to dynamically control pulse width and phase with respect to a reference signal. The pulse width and phase of each PWM waveform (with respect to the reference signal) can be independently adjusted over a 0° to 360° range with arbitrarily fine resolution that is not affected by the operating frequency. The generated PWM signals are capable of maintaining phase and frequency lock to the reference signal for a wide modulation range of the reference signal frequency. The concepts, systems, devices and techniques described herein are suitable for generating accurate and dynamically adjustable PWM waveforms for HF and VHF applications. They have particular value in applications in which a reference signal is derived from a radio frequency (RF) input source with respect to which precise timing of the PWM must be maintained, including phase-switched impedance modulation (PSIM) based tunable matching networks (TMNs) and PSIM amplifiers. Such circuits find application in high power microwave plasma systems for use in connection with semiconductor processing and cleaning of semiconductor processing equipment, for example.

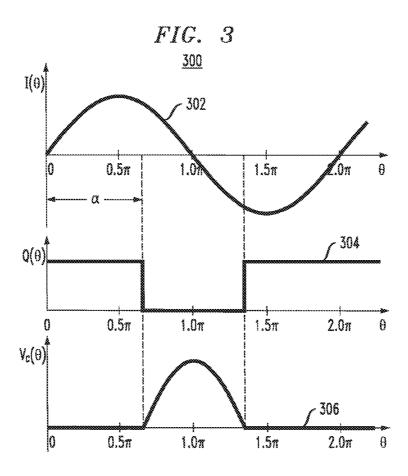

In one aspect of the concepts, systems, and techniques described herein, a pulse width modulation (PWM) generator includes a phase-shifting circuit that has at least one input and a plurality of outputs. The phase-shifting circuit is configured to receive a reference signal and, in response, provide a phase-shifted signal on each of said two or more outputs. Each phase-shifted signal can have a phase shift relative to the reference signal. The PWM generator can further include a waveform combiner. The waveform combiner can have a plurality of inputs with each input coupled to a respective output of the phase-shifting circuit. The waveform combiner can be configured to receive the phase-shifted signals from the phase-shifting circuit and, in response, generate a PWM signal having a pulse width and phase-shift relative to the reference signal.

With this arrangement, a PWM generator for generating a PWM signal with a pulse width and phase shift relative to a reference signal is provided. In embodiments, the pulse

•

width and phase shift relative to the reference signal of the PWM signal can be dynamically controlled. Because the waveform combiner is configured to generate the PWM in response to the phase-shifting signals, altering the phase-shifting signals may adjust the pulse width and phase shift 5 relative to the reference signal of the PWM signal.

In embodiments, the phase-shifting circuit can include a plurality of phase-shifting elements coupled in a parallel architecture or in a cascaded architecture.

In embodiments, the phase-shifting circuit can include an 10 In-phase/quadrature-phase (IQ) modulator having at least three inputs and at least one output. One input of the IQ modulator can be configured to receive the reference signal and two other inputs of the IQ modulator can be configured to receive baseband signals derived from the reference 15 signal. The IQ modulator can include an adder coupled between its output and at least two of its inputs.

In embodiments, the waveform combiner can include at least one of an edge detector, logic gate, flip-flop, or amplifier. The waveform combiner can also include a plurality of 20 amplifiers that each have an input and an output. Each input of the amplifiers can be configured to receive a phase-shifted signal. The waveform combiner can further include a logic gate that has a plurality of inputs and at least one output. Each input of the waveform combiner can be configured to 25 be coupled to the output of at least one amplifier.

In embodiments, phase-shifting circuit can be configured to generate two or more phase shifted signals based upon at least one predetermined phase-shift parameter. The phase-shifting circuit can also be configured to receive the at least 30 one predetermined phase-shift parameter from a controller. The controller can be configured to generate at least one predetermined phase-shift parameter based upon the pulse width and phase-shift relative to the reference signal of the generated PWM signal.

In embodiments, the PWM generator can be realized in an integrated circuit.

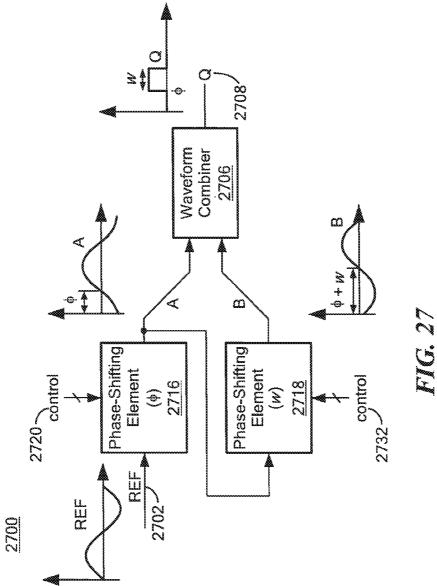

The PWM generation techniques presented herein rely on the use of phase-shifting elements that take an input waveform and generate an output waveform locked to the input 40 in both phase and frequency (or in both delay and frequency), The phase shift (or delay) between the input and the output can be dynamically controlled (via digital or analog methods), and the resolution with which the phase shift can be set ultimately determines the resolution with which one 45 can adjust the phase and pulse width of a PWM signal. These phase-shifting elements can be cascaded or connected in parallel to form cascaded or paralleled system architectures respectively.

In another aspect of the concepts, systems and techniques 50 described herein, an apparatus for generating dynamically controlled pulse width modulation (PWM) signals. The apparatus can include two or more phase-shifting elements. Each phase-shifting element can have an input and output with the input of each phase-shifting element that can be 55 configured to receive a reference signal. The apparatus can further include a waveform combiner that can be electronically coupled to the outputs of the phase-shifting elements. Each phase-shifting element can be configured to generate a respective phase-shifted signal at its output based upon the 60 reference signal and a respective predetermined phase-shift parameter. Also, the waveform combiner can be configured to generate a PWM signal having a pulse width and pulse shift based upon the phase-shifted signals generated at the outputs of the phase-shifting elements.

With this particular arrangement, a parallel architecture for generating a desired PWM signal is provided. In embodi4

ments, the PWM signal can have a dynamically adjustable pulse width and phase shift relative to the reference signal. By adjusting the phase-shift parameters of the phase-shifting elements, the pulse width and phase shift of the PWM signal can be dynamically controlled.

In embodiments, each predetermined phase-shift parameter can include at least one of a predetermined phase shift or a predetermined pulse width.

In embodiments, at least one of the phase-shifting elements can include an In-phase/Quadrature modulator or a phase-lock loop.

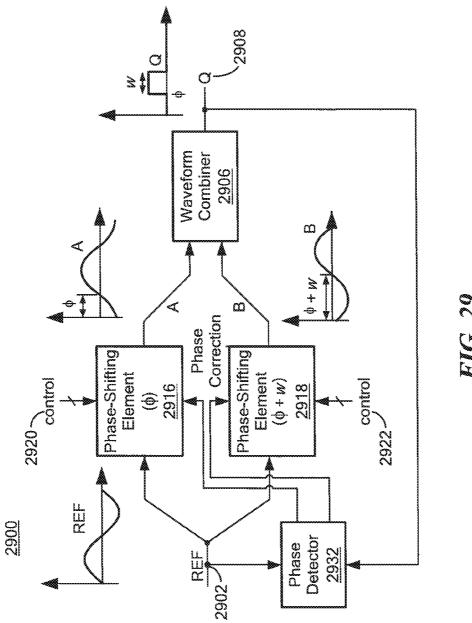

In embodiments, each phase-shifting element can be coupled to a respective control signal. Each respective control signal can include the respective predetermined phase shift parameter. The apparatus can further include a phase detector coupled to the reference signal and the generated PWM signal. In embodiments, the phase detector can be configured to generate a phase correction signal based upon a comparison of the reference signal to the generated PWM signal. The phase correction signal can be provided to each phase-shifting element.

In embodiments, the waveform combiner can include at least one edge detector, each edge detector being coupled to at least one flip-flop. The flip-flop can be configured to generate the PWM signal based upon a rising edge of at least one generated phase-shifted signal and a rising edge of at least one other generated phase-shifted signal.

In another aspect of the concepts, systems and techniques described herein, an apparatus for generating dynamically controlled pulse width modulation (PWM) signals is provided. The apparatus can include a first phase-shifting element having input and outputs. The input of the first phase-shifting element can be coupled to a reference signal. The apparatus can also include a second phase-shifting 35 element that can have an input and output. The input of the second phase shifting element can be coupled to the output of the first phase-shifting element. The apparatus can also include a waveform combiner that can be electronically coupled to the outputs of the first and second phase-shifting elements. The first phase-shifting element can be configured to generate a first phase-shifted signal at its output based upon the reference signal and a respective predetermined phase shift. The second phase-shifting element can be configured to generate a second phase-shifted signal at its output based upon the first phase-shifted signal and a respective predetermined phase shift. The waveform combiner can be configured to generate a PWM signal having a pulse width and pulse shift based upon the first and second phase-shifted signals.

With this particular arrangement, a cascaded architecture for generating a desired PWM signal is provided. In this arrangement, each phase-shifting element may receive a distinct, unrelated phase-shift parameter. Due to this, fewer phase-shift parameters may need to be adjusted to achieve a desired pulse width and phase-shift relative to the reference signal for the generated PWM signal.

In embodiments, each predetermined phase-shift parameter can include at least a predetermined phase shift or a predetermined pulse width.

In embodiments, at least one of the phase-shifting elements can include an In-phase/Quadrature modulator. The apparatus can also include a control circuitry coupled to the at least one In-phase/Quadrature modulator, said control circuitry configured to provide a control signal to the at least one In-phase/Quadrature modulator. In embodiments, the control signal can include a respective predetermined phase shift parameter for the In-phase/Quadrature modulator.

In embodiments, at least one of the phase-shifting elements comprises a phase-lock loop.

In embodiments, the apparatus can further include a phase detector that can be coupled to the reference signal and the generated PWM signal. The phase detector can be configured to generate a phase correction signal based upon a comparison of the reference signal to the generated PWM signal. In embodiments, each phase-shifting element can further be configured to generate a phase-shifted signal based upon the phase correction signal.

In embodiments, the waveform combiner can include at least one logic gate. The logic gate can be configured to compare the first and second phase-shifted signals.

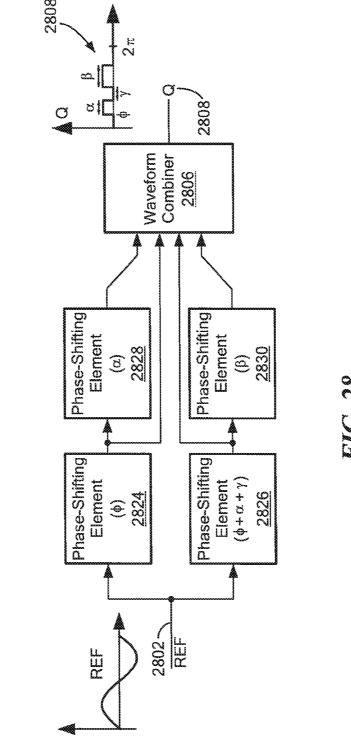

In still another aspect of the concepts, systems and techniques described herein, an apparatus for generating 15 dynamically controlled pulse width modulation (PWM) signals is described. The apparatus can include a first set of phase-shifting elements electronically coupled in parallel and each having an input and output. The inputs of the first set of phase-shifting elements can each electronically 20 coupled to a reference signal. The apparatus can also include a second set of phase-shifting elements electronically coupled in parallel and each having an input and output. The inputs of the second set of phase-shifting elements can each electronically coupled to the output of at least one phase- 25 shifting element of the first set. The apparatus can also include a waveform combiner electronically coupled to the outputs of the phase-shifting elements of the first and second sets. Each phase-shifting element of the first set can be configured to generate a respective phase-shifted signal at its 30 output based upon the reference signal and a respective predetermined phase shift. Each phase-shifting element of the second set can be configured to generate a respective phase-shifted signal at its output based upon at least one phase-shifted signal generated by a phase-shifting element 35 of the first set and a respective predetermined phase shift. The waveform combiner can be configured to generate a dual-pulse PWM signal having a first pulse with a pulse width and pulse shift based upon the phase-shifted signals generated by the phase-shifting elements of the first set. The 40 PWM signal can also have a second pulse with a pulse width and pulse shift based upon the phase-shifted signals generated by the phase-shifting elements of the second set.

With this particular arrangement, an architecture for generating a dual pulse PWM signal is provided. The dual pulse 45 PWM signal can have two pulse widths and phase shifts relative to a reference signal that can be dynamically adjusted. By having two pulse widths and phase shifts, multiple phase-switched reactance elements can be driven at once.

In embodiments, the phase-shifting elements of the first set can be electronically coupled in a parallel architecture. The inputs of each phase-shifting element of the first set can be coupled to the reference signal.

In embodiments, the phase-shifting elements of the first 55 set can be coupled in a cascading architecture

In still another aspect of the concepts, systems and techniques described herein a method for generating dynamically controlled pulse width modulation (PWM) waveforms is provided. The method can include receiving a 60 reference signal at one or more phase-shifting elements. Each phase-shifting element can have a respective predetermined phase-shift parameter. The method can also include generating respective phase-shifted signals at outputs of the one or more phase-shifting elements based upon 65 the reference signal and the respective predetermined phase shift parameters. The method can further include combining

6

the generated phase-shifted signals to obtain a PWM waveform having a pulse width and phase shift based upon the predetermined phase shift parameters of the phase-shifting elements

With this particular arrangement, a method for generating a PWM signal with dynamically controlled pulse widths and phase shifts relative to a reference signal is provided. By adjusting the phase-shift parameters, the pulse width and phase shifts of the PWM signal can be dynamically controlled

In embodiments, each respective predetermined phase shift parameter can include at least one of a respective predetermined phase shift or respective predetermined pulse width.

In embodiments, the method can further include providing a respective control signal to each phase-shifting element. The control signal can include the respective predetermined phase shift parameter.

In embodiments, the method can also include generating a phase correction signal based upon a comparison of the reference signal to the PWM waveform.

In embodiments, the method can further include adjusting the generated phase-shifted signals based upon the phase correction signal.

In still another aspect of the concepts, systems and techniques described herein a power generation and delivery system having an input port and an output port is provided. The power generation and delivery system can include a pulse width modulation (PWM) signal generator that can include one or more phase-shifting elements. The PWM signal generator can be to generate a PWM signal based upon a phase-shifting elements. The power generation and delivery system can also include a phase-switched tunable impedance network coupled to the output port. The phase-switched tunable impedance network can be configured to receive a generated PWM signal from the PWM signal generator, and, in response, can vary an impedance thereof to modulate an impedance presented to the output port.

With this particular arrangement, a phase-switched tunable impedance (PSIM) network driven by a PWM signal is provided. Because the PWM signal generated by the PWM generator can have its pulse width or phase shift relative to a reference signal dynamically adjusted, these parameters may be adjusted in order to change the impedances presented by the PSIM.

In embodiments, the one or more phase-shift elements are electronically coupled in a parallel architecture or cascading architecture.

# BRIEF DESCRIPTION OF THE DRAWING FIGURES

Other aspects, features, and advantages of the broad concepts sought to be protected herein will become more fully apparent from the following detailed description, the appended claims, and the accompanying drawings in which like reference numerals identify similar or identical elements. Reference numerals that are introduced in the specification in association with a drawing figure may be repeated in one or more subsequent figures without additional description in the specification in order to provide context for other features.

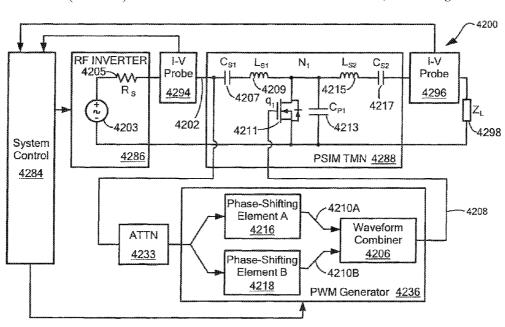

FIG. 1 is a block diagram of an illustrative tunable impedance matching network (TMN) in accordance with described embodiments;

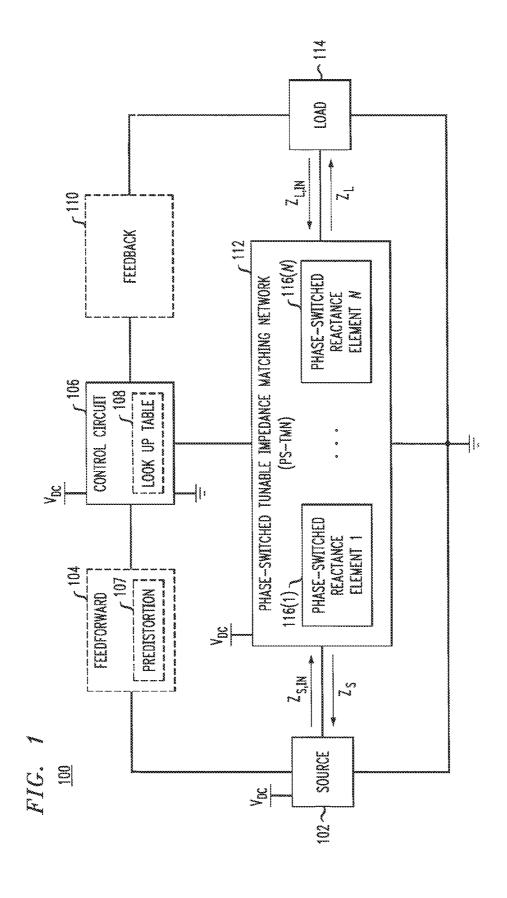

- FIG. 2 is a schematic diagram of an illustrative phase-switched variable capacitance element of the TMN of FIG. 1.

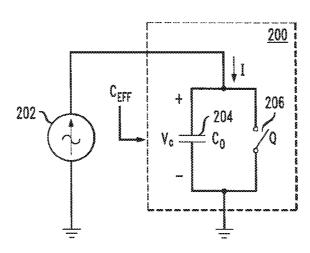

- FIG. 3 is a plot of current and voltage versus phase with respect to a control signal of the phase-switched variable 5 capacitance element of FIG. 2;

- FIG. 4 is a schematic diagram of an illustrative phase-switched variable inductance element of the TMN of FIG. 1;

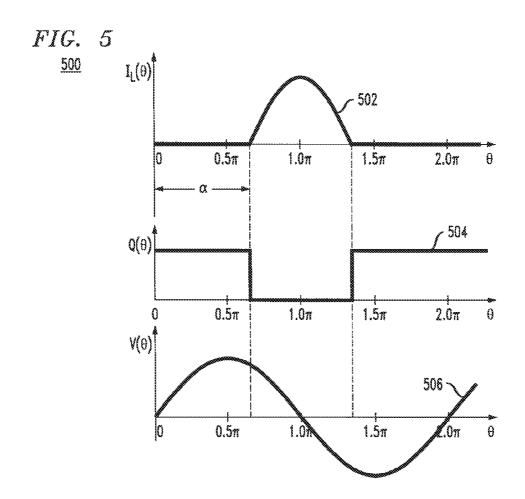

- FIG. 5 is a plot of current and voltage versus phase with respect to a control signal of the phase-switched variable 10 inductance element of FIG. 4;

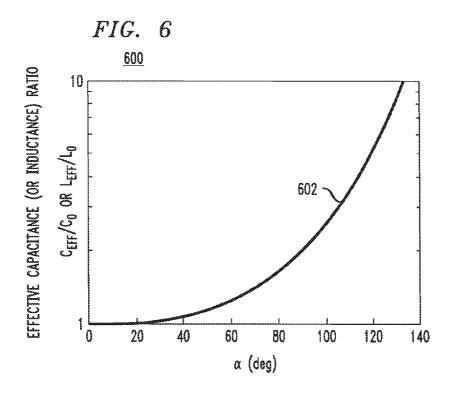

- FIG. 6 is a plot of normalized effective capacitance (or inductance) of the phase-switched elements of FIGS. 2 and 4 versus a control angle of the phase-switched element;

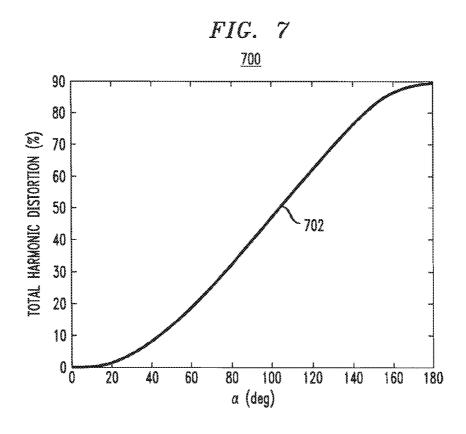

- FIG. 7 is a plot of total harmonic distortion of the 15 phase-switched elements of FIGS. 2 and 4 versus the control angle of the phase-switched element;

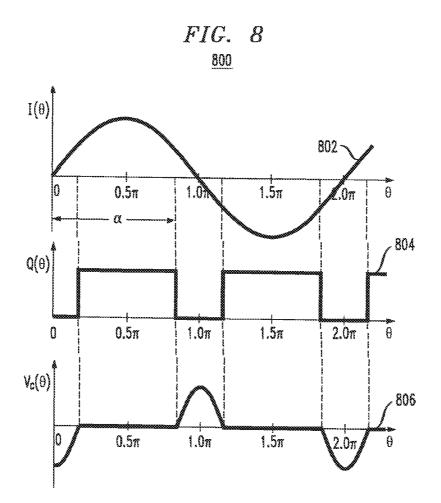

- FIG. 8 is a plot of current and voltage versus phase with respect to a control signal of a full-wave switched variable capacitance element:

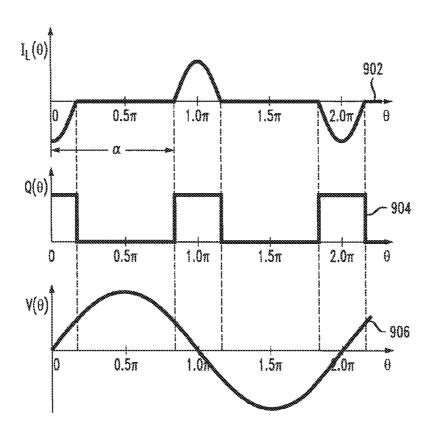

- FIG. 9 is a plot of current and voltage versus phase with respect to a control signal of a full-wave switched variable inductance element;

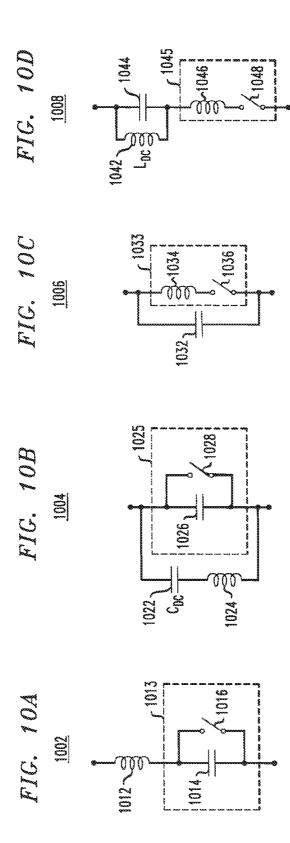

- FIGS. **10**A-D are schematic diagrams of illustrative switched reactance elements in accordance with described 25 embodiments;

- FIG. 11 is a schematic diagram of an illustrative phaseswitched tunable matching network (TMN) employing a digitally-switched capacitance matrix;

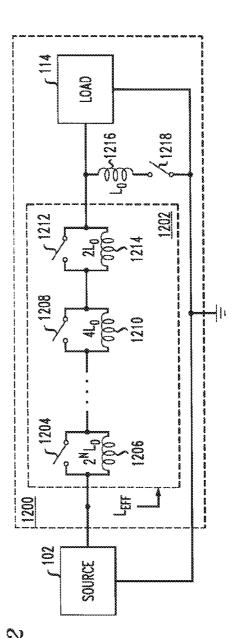

- FIG. 12 is a schematic diagram of an illustrative phase- 30 switched TMN employing a digitally-switched inductance matrix;

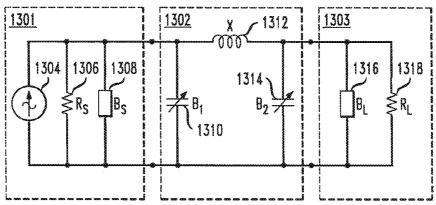

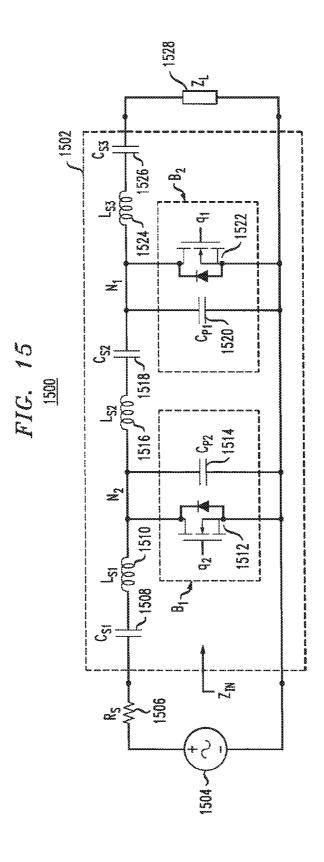

- FIG. 13 is a schematic diagram of an illustrative phase-switched TMN in accordance with described embodiments;

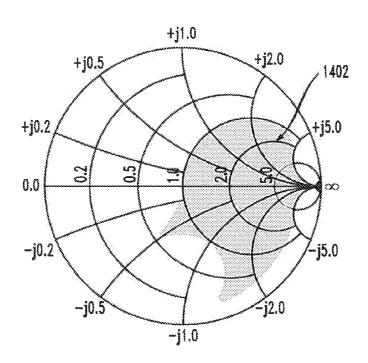

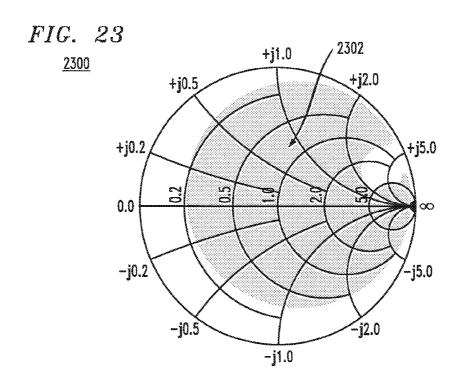

- FIG. **14** is a Smith chart of a range of load impedances that can be matched by the tuning network of FIG. **13** for an illustrative operating range;

- FIG. 15 is a schematic diagram of additional detail of the tuning network of FIG. 13;

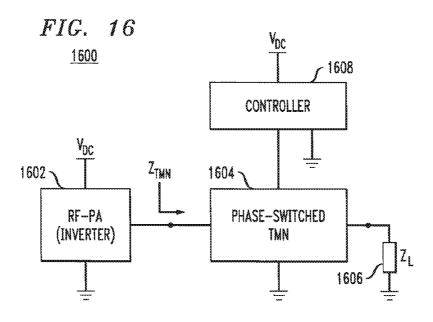

- FIG. **16** is a block diagram of an illustrative topology of a phase-switched impedance modulation amplifier in accordance with described embodiments;

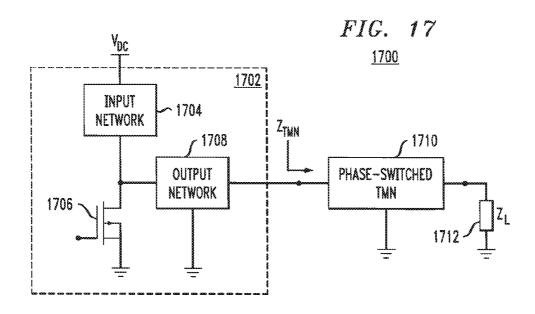

- FIG. 17 is a block diagram of another illustrative topology of a phase-switched impedance modulation amplifier in accordance with described embodiments;

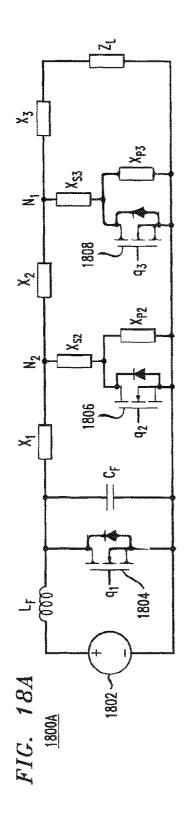

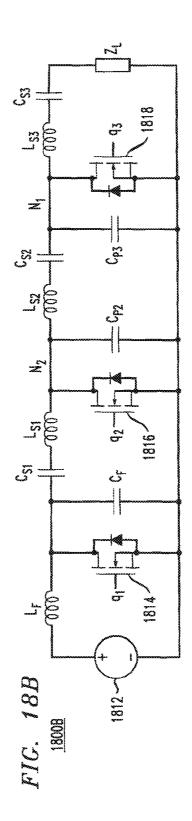

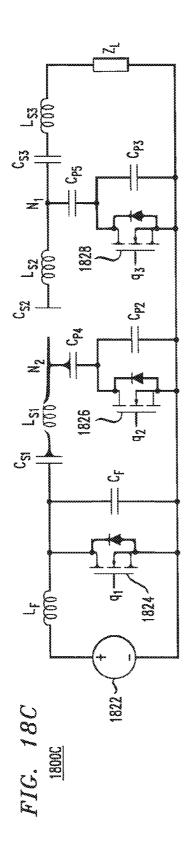

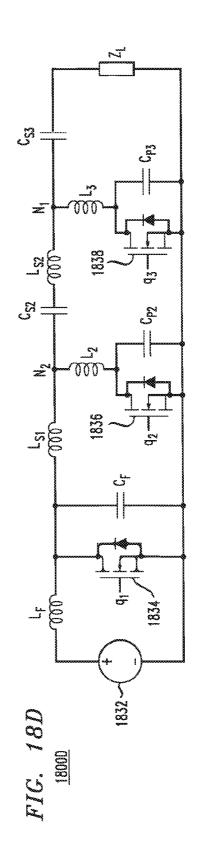

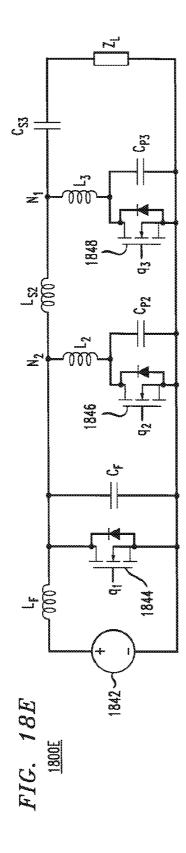

- FIGS. **18**A-E are schematic diagrams of illustrative threeswitch phase-switched impedance modulation amplifiers in accordance with described embodiments:

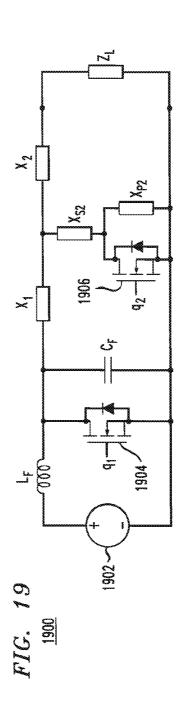

- FIGS. 19 and 20 are schematic diagrams of illustrative two-switch phase-switched impedance modulation amplifiers in accordance with described embodiments;

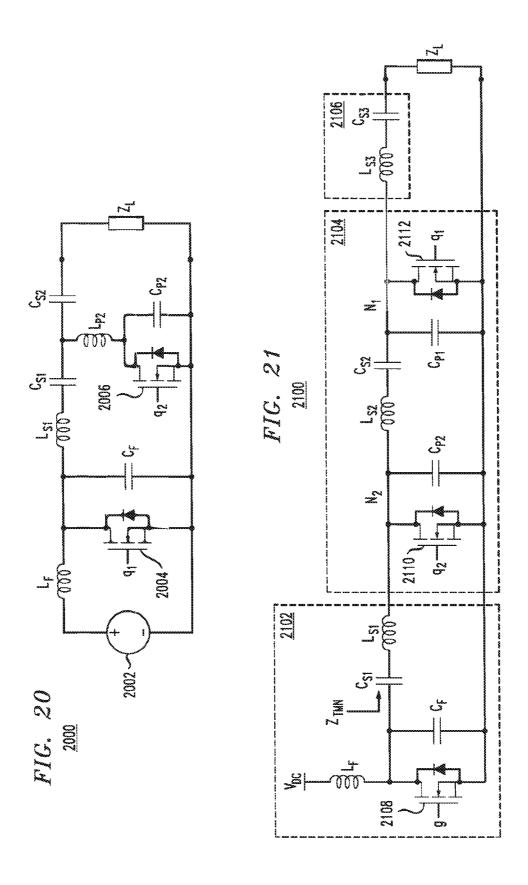

- FIG. 21 is a schematic diagram of an illustrative phaseswitched impedance modulation amplifier over an illustrative operating range;

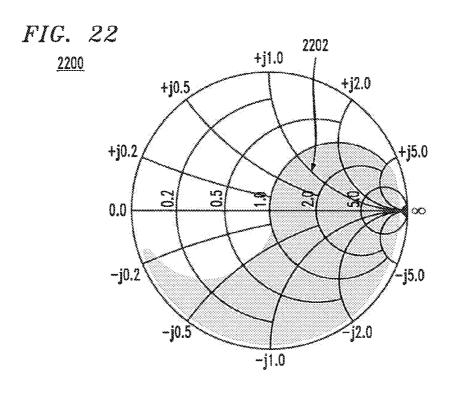

- FIGS. 22 and 23 are Smith charts showing a range of load impedances that can be matched by the phase-switched impedance modulation amplifier of FIG. 21 for an illustrative operating range;

- FIG. **24** is a flow diagram of an illustrative process of operating a TMN;

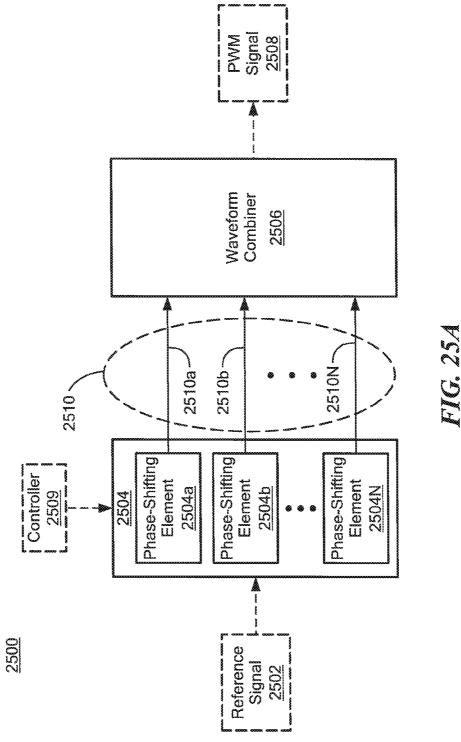

- FIG. **25**A is a block diagram of a system for generating pulse width modulated (PWM) signals having predetermined phase shifts and pulse widths;

- FIG. **25**B is a plot of a pulse width modulated (PWM) waveform having pulse width w and a phase shift φ relative to a reference signal with the PWM signal being in phase and frequency lock with the reference signal;

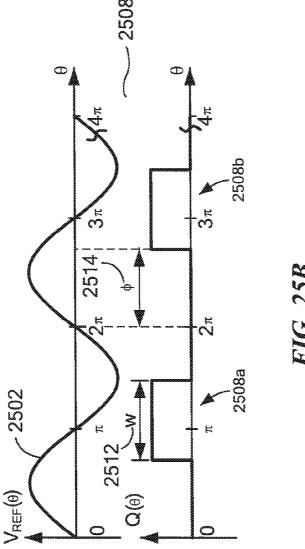

- FIG. 26 is a block diagram of a PWM generation circuit having a parallel architecture;

- FIG. 27 is a block diagram of a PWM generation circuit having a cascade architecture;

- FIG. **28** is a block diagram of a PWM generator circuit having a dual-pulse PWM generation architecture;

- FIG. **29** is a block diagram of a PWM generation circuit having a parallel PWM generation architecture with two phase-shifting elements and a phase detector feedback loop;

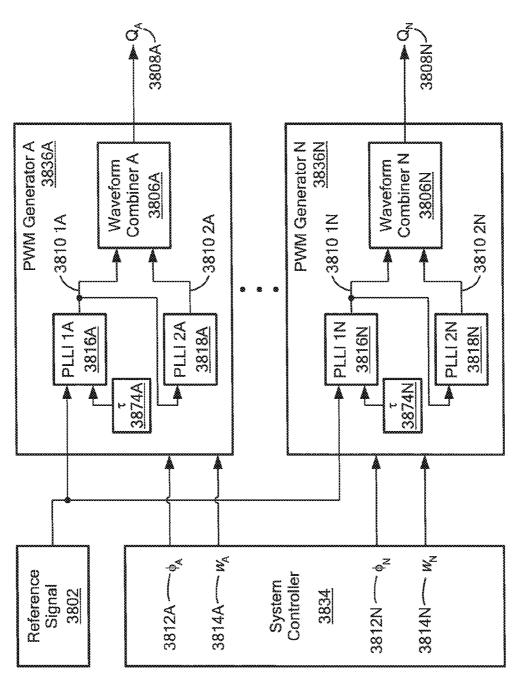

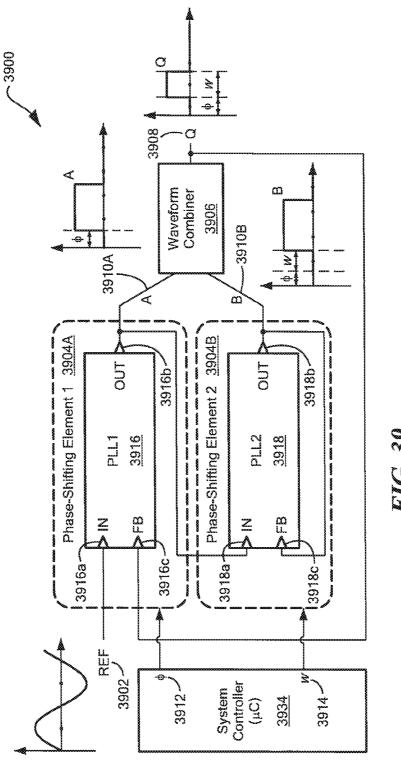

- FIG. 30 is a block diagram of a system having an architecture capable of generating multiple PWM waveforms that are phase- and frequency-locked to a common reference signal;

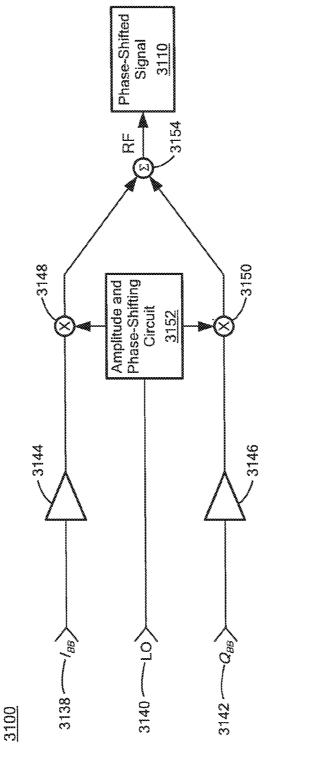

- FIG. 31 is a block diagram of a PWM generation circuit having an in-phase/quadrature-phase (IQ) modulator;

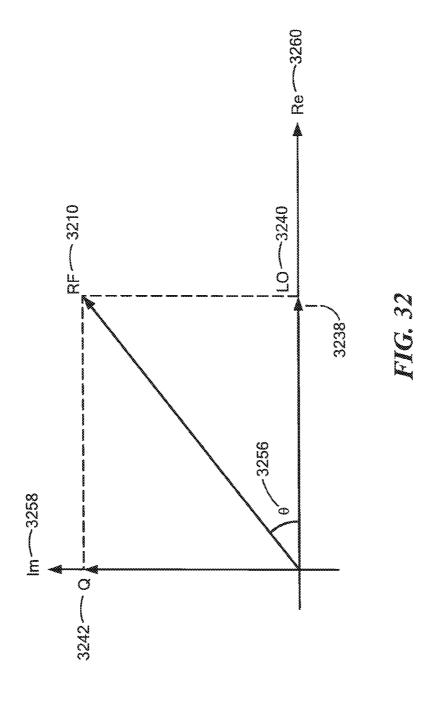

- FIG. 32 is a phase diagram illustrating a phase shift according to baseband inputs of an IQ modulator;

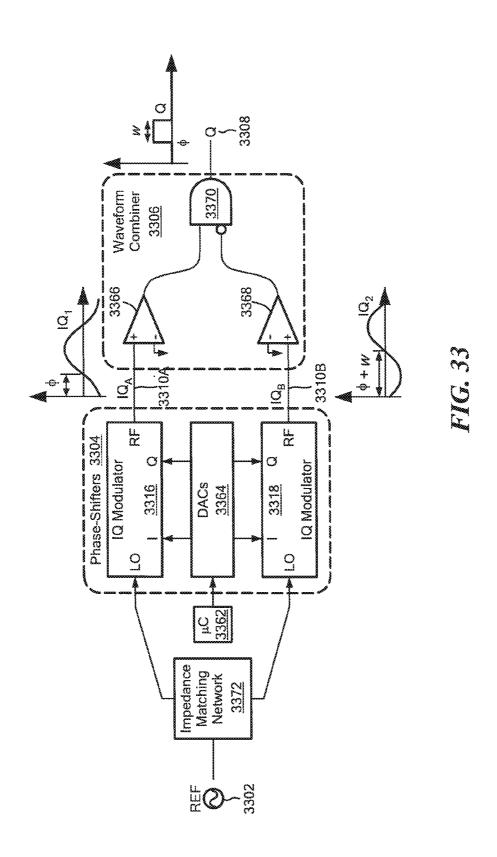

- FIG. 33 is a block diagram of a PWM generation circuit having a parallel PWM generation architecture with two phase-shifters implemented as IQ modulators;

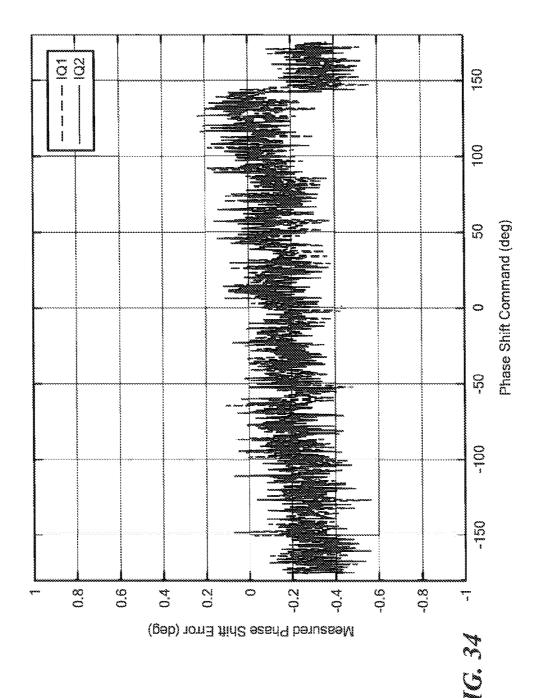

- FIG. 34 is a plot of phase shift command vs. measured phase shift error for a pair of output signals from respective ones of IQ modulators of the PWM generation circuit of FIG. 33;

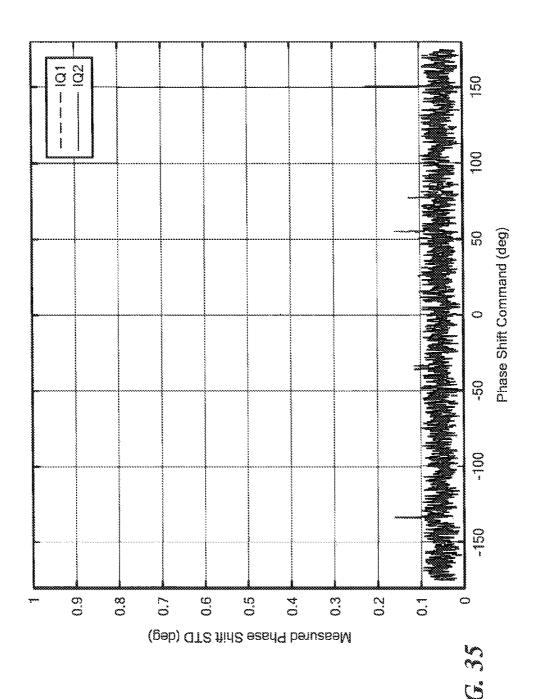

- FIG. 35 is a plot of phase shift command vs. measured phase shift standard deviation for a pair of output signals from respective ones of IQ modulators of the PWM generation circuit of FIG. 33;

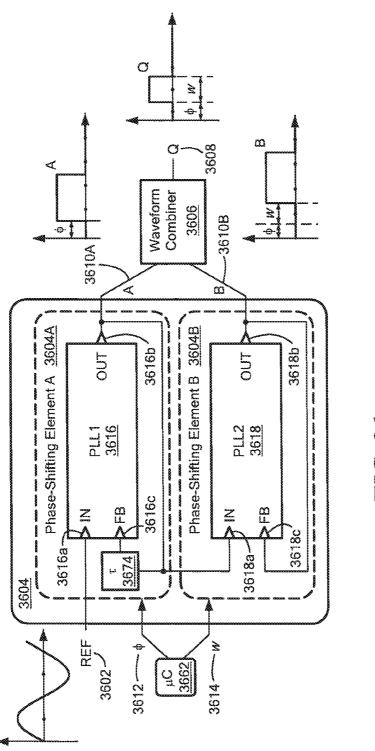

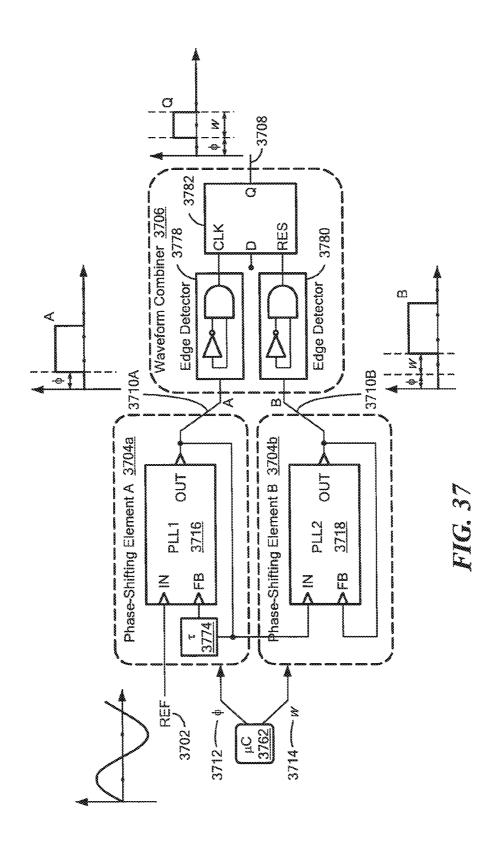

- FIG. **36** is a block diagram of a cascaded PWM waveform generator having phase-shifting elements implemented using phase-locked loop (PLL) modules coupled to a waveform combiner;

- FIG. 37 is a block diagram of the cascaded phase-locked PWM generator of FIG. 36 having a waveform combiner provided from a D-type flip-flop and edge detectors;

- FIG. 38 is a block diagram of a PWM signal generation system implemented with a PLL;

- FIG. **39** is a block diagram of a PWM generation system having a nested PLL architecture with feedback;

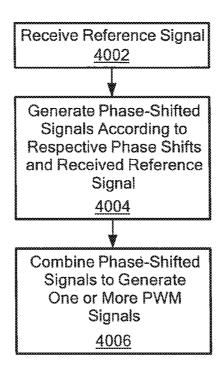

- FIG. 40 is a flowchart of a method of generating PWM signals with desired phase shifts and pulse widths;

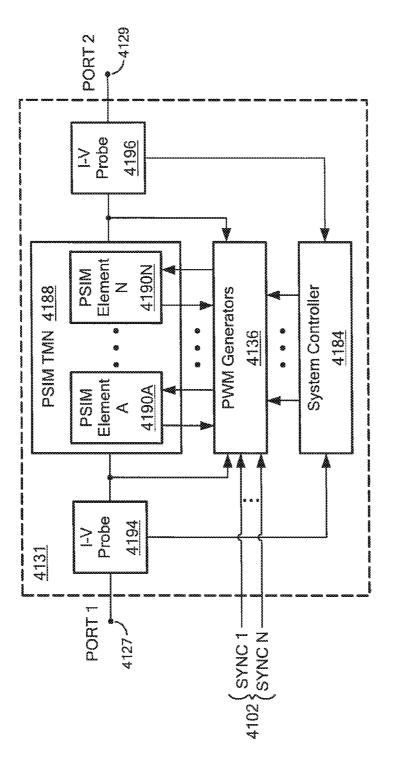

- FIG. **41**A is a block diagram of an impedance matching system comprising a plurality of phase-switched, impedance (PSIM) elements driven by PWM generators;

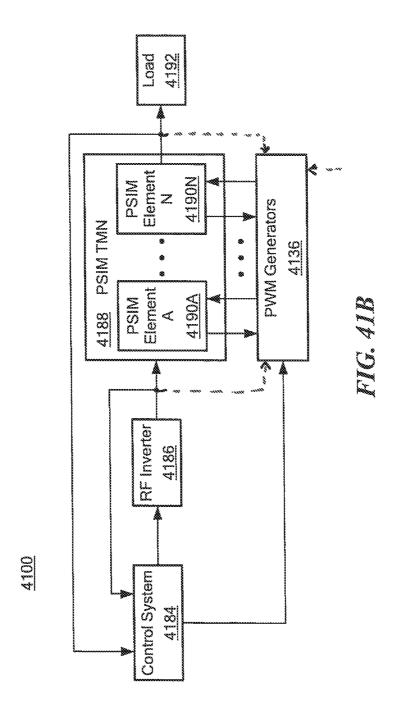

- FIG. 41B is a block diagram of a radio frequency ("RF") amplifier having a phase-switched tunable impedance network coupled to a system for generating PWM signals with desired phase shifts and pulse widths;

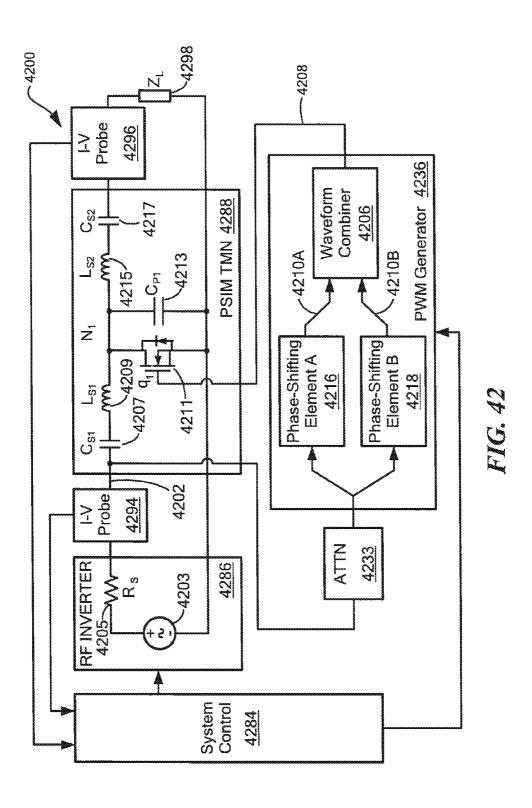

- FIG. **42** is a block diagram of a system having a phase-switched tunable impedance network having one phase-switched tunable impedance element coupled to a PWM generator; and

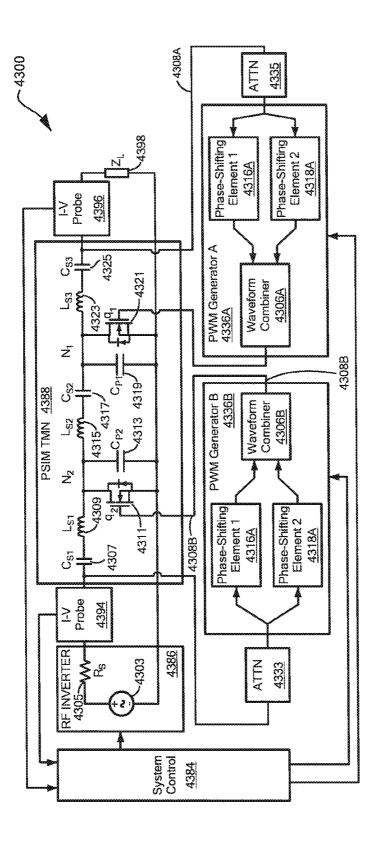

- FIG. **43** is a block diagram of a system having a phase-switched tunable impedance network having two phase-switched tunable impedance elements coupled to two PWM generators.

### DETAILED DESCRIPTION

Table 1 summarizes a list of acronyms employed throughout this specification as an aid to understanding the described embodiments:

#### TABLE 1

CMOS Complementary Metal-Oxide Semiconductor Cognitive Radio

| FET  | Field Effect<br>Transistor             | HEMT   | High-Electron-<br>Mobility Transistor                   |  |  |  |

|------|----------------------------------------|--------|---------------------------------------------------------|--|--|--|

| IC   | Integrated<br>Circuit                  | LUT    | Look Up Table                                           |  |  |  |

| MEMS | Micro-Electro-<br>Mechanical Systems   | PA     | Power Amplifier                                         |  |  |  |

| PSIM | Phase-Switched<br>Impedance Modulation | PS-TMN | Phase-Switched<br>Tunable impedance<br>Matching Network |  |  |  |

| RF   | Radio Frequency                        | SDR    | Software Defined Radio                                  |  |  |  |

| TMN  | Tunable impedance<br>Matching Network  | WPT    | Wireless Power Transfer                                 |  |  |  |

| ZCS  | Zero Current Switching                 | ZVS    | Zero Voltage Switching                                  |  |  |  |

Described embodiments are directed toward phaseswitched, tunable matching networks (PS-TMNs) and phase-switched, impedance modulation amplifiers (PSIMs). Both the phase-switched, tunable matching networks and the phase-switched, impedance modulation amplifiers include phase-switched variable network reactance elements. When 20 configured in the context of PS-TMNs and phase-switched, impedance modulation amplifiers, such phase-switched variable network reactance elements provide rapid, high bandwidth, continuous impedance matching over a wide impedance range, while operating efficiently at high power 25 levels without requiring high bias voltages or currents. PS-TMNs might be employed alone, or might also be employed in combination with other matching techniques such as discrete switched reactance banks.

PS-TMNs might be employed in a variety of reconfigurable and adaptive RF systems, for example, RF front ends for software-defined radio (SDR) and cognitive radio (CR) applications that operate over a wide range of frequency bands, at different bandwidths, and in accordance with a variety of communication standards. PS-TMNs might also 35 be employed in other RF applications, such as drivers for RF plasma loads to compensate for rapid load variations, or in wireless power transfer (WPT) systems to compensate for impedance mismatches between the transmitter and receiver to maximize transferred power and/or efficiency.

The PSIMs may be operable as zero voltage switching (ZVS) radio frequency (RF) amplifiers. Such PSIM amplifiers might employ a PS-TMN to operate over a large frequency range by efficiently modulating output power over a wide frequency range and/or matching into highly variable 45 loads (e.g., loads that are variable over a wide impedance range).

Referring to FIG. 1, a radio frequency (RF) system 100 includes a phase-switched tunable impedance matching network (PS-TMN) 112 coupled between a source 102, having 50 an impedance  $Z_S$ , and a load 114, having an impedance  $Z_L$ . In some applications, source 102, control circuit 106 and PS-TMN 112 (and other elements of RF system 100) are coupled to a power supply voltage (e.g.,  $\mathbf{V}_{DC}$ ) and ground. Control circuit 106 is coupled to PS-TMN 112 and provides 55 control signals to PS-TMN 112 so as to control operation of PS-TMN 112. In response to such control signals, PS-TMN 112 provides a desired impedance transformation characteristic. It should be appreciated that control circuit 106 might be an internal component to PS-TMN 112, or might be an 60 external component coupled to PS-TMN 112 or some portions of control circuit 106 (or functions provided by control circuit 106 may be internal to PS-TMN 112 while other portions of control circuit 106 may be external to PS-TMN 112)

In some embodiments, control circuit 106 controls operation of PS-TMN 112 based, at least partially, upon informa-

10

tion received from an optional feedforward circuit 104 coupled to source 102 and/or an optional feedback circuit 110 coupled to load 114. In some embodiments, optional feedforward circuit 104 includes adaptive predistortion circuit 107 and control circuit 106 includes look up table (LUT) 108. For example, as will be described in greater detail below, some embodiments might employ one or more nonlinear control techniques (e.g., by control circuit 106) to determine appropriate control signals for PS-TMN 112, such 10 as employing fixed or adaptable look-up tables (e.g., LUT 108) to store predetermined control signal information, feedback (e.g., by feedback circuit 110) and/or feedforward compensation (e.g., by feedforward circuit 104) to adaptively adjust control signal information, or performing digital predistortion of the control signals (e.g., by predistortion circuit 107), or other similar techniques.

PS-TMN 112 includes one or more phase-switched reactance elements 116(1)-116(N). As will be described in greater detail below, phase-switched reactance elements 116(1)-116(N) might be implemented using one or more capacitive elements (e.g., capacitors), one or more inductive elements (e.g., inductors), or a combination of both. Phaseswitched reactance elements 116(1)-116(N) can be controlled to adjust the effective impedance ( $Z_{S,I\!N}$  and  $Z_{L,I\!N}$ ) presented to the terminals of PS-TMN 112 at a desired frequency. The phase-switched reactance elements 116(1)-116(N) are switched, for example by either a shunt or a series switch, and the effective impedance of the phaseswitched reactance elements is controlled by adjusting the phase and/or duty-cycle of the shunt or series switch. In some embodiments, the desired frequency might be the RF frequency of operation of RF source 102 (e.g., the frequency of the signal provided from RF source 102 to PS-TMN 112).

By modulating the effective impedance at a desired frequency of operation of RF system 100 (e.g., by adjusting the impedance of phase-switched reactive elements 116(1)-116 (N)), it is possible to adjust, tune, change or otherwise manipulate the impedance presented by PS-TMN 112 to source 102 and/or load 114. For example, phase-switched reactance elements 116(1)-116(N) allow PS-TMN 112 to present a desired impedance ( $Z_{S,IN}$ ) to PS-TMN 112 from source 102 and a desired impedance ( $Z_{L,IN}$ ) into PS-TMN 112 from load 114.

The control signals provided to PS-TMN 112 operate to control the timing of turning on and/or off the switches of phase-switched reactance elements 116(1)-116(N) with respect to the RF signal provided from source 102. The switching provides the effective reactance values of phase-switched reactance elements 116(1)-116(N) that effect the desired impedance transformation of PS-TMN 112. Feed-forward information might include information about the effective input impedance of PS-TMN 112, the timing of RF waveforms, specified signal levels and/or impedance levels, etc. Feedback information might include measured information about the effective load impedance and/or power reflected from the load, the timing of RF waveforms, etc.

Thus, in some embodiments, PS-TMN 112 might be employed to provide a desired impedance transformation between source 102 and load 114. For example, PS-TMN 112 might provide an impedance match between source 102 and load 114. Alternatively, the impedance of PS-TMN 112 might be adjusted to compensate for variations in the impedance ( $Z_L$ ) of load 114 such that source 102 is coupled to a more stable impedance (e.g.,  $Z_{S,IN}$ ) provided by PS-TMN 112.

Referring to FIG. 2, sinusoidal current source 202, having a current I, drives an illustrative phase-switched variable

reactance 200. The phase-switched variable reactance is here shown as including a parallel combination of a capacitor 204 and switch 206 to provide the phase-switched variable reactance as phase-switched variable capacitance 200. Capacitor 204 has a physical capacitance C<sub>0</sub>, and a voltage  $V_C$ . The state of switch 206 is controlled by a characteristic of signal Q. For example, switch 206 provides a low impedance signal path between its terminals (e.g., switch 206 is "on" or "closed") when signal Q has a logic high value, and switch 206 provides a high impedance signal path between its terminals (e.g., switch 206 is "off" or "open") when signal Q has a logic low value. Thus, switch 206 could be considered to switch capacitor 204 into the circuit when the switch is open (current I flows into capacitor 204), and out of the circuit when the switch is closed (current I flows 15 through the closed switch and bypasses capacitor 204).

If switch 206 is always off (open), then the effective capacitance, C<sub>EFF</sub>, of phase-switched variable capacitance 200 presented to source 202 is equivalent to the physical capacitance, Co, of capacitor 204. Alternatively, if switch 20 206 is always on (closed), then the low impedance path between the terminals of switch 206 effectively "shorts" capacitor 204, and phase-switched variable capacitance 200 behaves as an infinite capacitor in the sense that the voltage across capacitor 204 remains zero irrelevant of current I. The 25 effective capacitance, C<sub>EFF</sub>, of capacitor 204 can theoretically be controlled between  $C_0$  and infinity by controlling the conduction angle of switch 206 over an AC cycle of sinusoidal current source 202 from 0 to  $2\pi$ . As used herein, a conduction angle is the angle of the sinusoidal signal at 30 which switch 206 is turned on. The conduction angle with which the switch is turned on may be entirely determined by a switching signal Q (e.g., the switching angle) or partly determined by switching signal Q and partly by circuit waveforms such as voltage  $\mathbf{V}_{\mathcal{C}}$  and current I.

Referring to FIG. 3, illustrative waveforms of the current I and capacitor voltage  $V_C$  (e.g., the voltage of capacitor 204) are shown with respect to the switch control signal, Q, as a function of a cycle angle  $\theta$ . In particular, curve 302 shows  $I(\theta)$ , curve 306 shows  $V_C(\theta)$  and curve 304 shows 40  $Q(\theta)$  for a half-wave switched capacitor. As shown in FIG. 3, every cycle of  $I(\theta)$ , switch 206 is turned off (opened) a radians after  $I(\theta)$  transitions from negative to positive (e.g., switch 206 is on/closed until a radians into the positive half-cycle of  $I(\theta)$ ). Switch 206 remains off (open) until after 45 the capacitor voltage rings down to zero. Biasing the switch into its conductive state (e.g., turning the switch on or closing the switch) after the capacitor voltage rings down to zero ensures zero-voltage-switching (ZVS) turn on of switch 206.

If the switch includes a diode that naturally prevents the voltage from going negative, the timing of actively turning switch Q on may be relaxed, since it will naturally commutate "ON" when the switch voltage reaches zero and the active turn-on signal can be issued while the diode conducts. 55 The capacitor  $C_0$  across the switch provides snubbing of the turn off transition, providing zero-voltage-switching (ZVS) turn off of switch 206.

As shown in FIG. 3, when  $I(\theta)$  is a purely sinusoidal current source, switch **206** remains off (open) until the 60 conduction angle of the switch is reached (e.g., at  $2\alpha$ ). Thus, for a half-wave switched capacitor, switch **206** is turned on and off once per cycle of the RF signal from source **102** (e.g.,  $I(\theta)$  as shown by curve **302**).

Adjusting a sets where in the cycle switch 206 turns on 65 and off (e.g., controls the conduction angle of switch 206) and hence controls the voltage at which the capacitor peaks.

12

Thus, there is a relationship between the switching angle  $(\alpha)$  and the magnitude of the fundamental component of  $V_C(\theta)$  at the switching frequency. Consequently, the effective capacitance,  $C_{EFF}$ , of capacitor **204** can be represented as a function of a:

$$C_{EFF} = \frac{C_0 \cdot \pi}{\pi - \alpha + \sin(\alpha) \cdot \cos(\alpha)}$$

(1a)

Referring to FIG. 4, it is also possible to implement a phase-switched variable reactance as a switched inductor network that allows continuous control of its effective inductance at the switching frequency. Such a switched inductor network is shown in FIG. 4 as phase-switched variable inductance 400 and corresponds to the topological dual of the switched capacitor network 200 shown in FIG. 2. As shown in FIG. 4, illustrative phase-switched variable inductance 400 includes a series combination of inductor 404 and switch 406 being driven by a sinusoidal voltage source 402 with a voltage V. Inductor 404 has a physical inductance  $L_0$ , and an inductor current  $I_L$ . The state of switch 406 is controlled by the signal Q, for example, switch 406 might be on (e.g., closed) when signal Q has a logic high value, and off (e.g., open) when signal Q has a logic low value. Thus, switch 406 could be considered to switch inductor 404 into the circuit when the switch is closed (applying voltage V to inductor 404), and out of the circuit when the switch is open (no voltage is applied to inductor 404).

Similarly to the switched-capacitor implementation of a phase-switched variable reactance described in regard to FIG. 2, the effective inductance L<sub>EFF</sub> of phase-switched variable inductance 400 at the switching frequency can be modulated from a base value L<sub>0</sub> to infinity. For example, if switch 406 is always on (closed), then the effective inductance, L<sub>EFF</sub>, of phase-switched variable inductance 400 seen by source 402 is equivalent to the physical inductance, L<sub>0</sub>, of inductor 404. Alternatively, if switch 406 is always off (open), then inductor 404 behaves as an infinite inductor in the sense that the current through inductor 404 remains zero irrelevant of voltage V. The effective inductance, L<sub>EFF</sub>, of inductor 404 can ideally be controlled between L<sub>0</sub> and infinity by controlling the conduction angle of switch 406 over an AC cycle of sinusoidal voltage source 402 from 0 to

Referring to FIG. 5, illustrative waveforms of the current I and voltage  $V_{\mathcal{C}}$  of capacitor 204 are shown with respect to the switch control signal, Q, as a function of a cycle angle  $\theta$ . As a result of the properties of topological duality, the voltage waveform of the switched capacitor network shown in FIG. 3 is analogous to the current waveform of the switched inductor network shown in FIG. 5, and vice versa.

In particular, curve **502** shows  $I_L(\theta)$ , curve **506** shows  $V(\theta)$  and curve **504** shows  $Q(\theta)$  for a half-wave switched inductor. As shown in FIG. **5**, every cycle of  $V(\theta)$ , switch **406** is turned on (closed) a radians after  $V(\theta)$  transitions from negative to positive (e.g., switch **406** is off/open until a radians into the positive half-cycle of  $V(\theta)$ ). Switch **406** remains on (closed) until after the inductor current rings down to zero. Since the switch has an inductor in series with it, zero-current-switching (ZCS) turn on of the switch can be achieved. Turning the switch off at the time when the inductor current rings down to zero ensures zero-current-switching (ZCS) turn off of switch **406**. In duality with the capacitive circuit, utilization of diode(s) as part of switch Q

can enable natural commutation (turn off) of the switch and relax detailed active timing of the turn-off moment of the switching control waveform. As shown in FIG. 5, when  $V(\theta)$  is a purely sinusoidal voltage source, switch 406 remains on (closed) until the conduction angle of the switch is reached (e.g., at  $2\alpha$ ).

Adjusting a sets where in the cycle switch 406 turns on and off (e.g., controls the conduction angle of switch 406) and hence controls the current at which the inductor peaks. Thus, similarly to the switched-capacitor implementation of a phase-switched variable reactance described in regard to FIG. 2, there is a relationship between the switching angle ( $\alpha$ ) and the magnitude of the fundamental component of  $I_L(\theta)$  at the switching frequency. Consequently, the effective inductance,  $I_{EFF}$ , of inductor 404 can be represented as a function of  $\alpha$ :

$$L_{EFF} = \frac{L_0 \cdot \pi}{\pi - \alpha + \sin(\alpha) \cdot \cos(\alpha)}$$

(1b)

As a result of topological duality, expression (1b) for the effective inductance is the same as that of expression (1a) for the effective capacitance. Expression (1a) is consistent with the intuitive expectation for infinite effective capacitance when the switch is always in the on state  $(\alpha=\pi)$  and predicts the equivalence between  $C_{EFF}$  and  $C_0$  when the switch is permanently off  $(\alpha=0)$ . Expression (1b) is similarly consistent with the intuitive expectation for infinite effective inductance when the switch is always in the off state  $(\alpha=0)$  and predicts the equivalence between  $L_{EFF}$  and  $L_0$  when the switch is permanently on  $(\alpha=\pi)$ . Thus, in accordance with expressions (1a) and (1b), the effective capacitance  $C_{EFF}$  or the effective inductance  $L_{EFF}$  at the switching frequency can be modulated by controlling the conduction angle of the switch associated with the capacitor or inductor.

Referring to FIG. 6, the normalized effective capacitance,  $C_{EFF}/C_0$ , or the normalized effective inductance  $L_{EFF}/L_0$ , is 40 shown by curve 602 at the switching frequency. For the capacitive circuit this is the same thing as the normalized admittance  $Y_{EFF}/Y_0$  while for the inductive circuit this is the same as the normalized reactance,  $X_{EFF}/X_0$ . As a result of topological duality, the normalized effective admittance 45  $Y_{EFF}/Y_0$  of the phase-switched capacitor circuit of FIG. 2 is the same as the normalized reactance,  $X_{EFF}/X_0$  of the phased-switched inductor network shown in FIG. 4.

As shown in FIG. 6, the normalized effective capacitance  $C_{EFF}$  (or inductance  $L_{EFF}$ ) increases rapidly with a and 50 approaches infinity as  $\alpha$  approaches  $\pi$  (e.g., 180 degrees).

Referring to FIG. 7, curve 702 shows the total harmonic distortion of the capacitor voltage (inductor current) versus a for a purely sinusoidal current (voltage) excitation source. The practical range over which  $C_{EFF}$  or  $L_{EFF}$  can be modulated depends on the amount of harmonic distortion that can be present in the network. As a increases towards  $\pi$  (e.g., the conduction angle of the switch increases), the ringing of the capacitor voltage  $V_C$  (e.g., curve 306) or of the inductor current  $I_L$  (e.g., curve 502) is limited to a shorter time period. 60 As shown in FIG. 7, this results in significant harmonic content of the capacitor voltage for large  $Y_{\it EFF}/Y_0$  or  $X_{\it EFF}/Y_0$  $X_0$  (e.g.,  $C_{EFF}/C_0$  or  $L_{EFF}/L_0$ ) ratios (e.g., the total harmonic distortion increases as a increases). The amount of harmonic distortion allowed in a given system depends on specified 65 limits of harmonic content allowed into the source and/or load and the amount of filtering that is necessary or desired.

14

Note that FIG. 7 shows the harmonic distortion of the phase-switched variable reactance (e.g., the harmonic distortion of the capacitor voltage of phase-switched variable capacitance 200, or the harmonic distortion of the inductor current of phase-switched variable inductance 400), and not the harmonic content that is actually injected into the source and/or load of the RF system (e.g., source 102 and load 114). In some embodiments, the phase-switched variable reactance (e.g., phase-switched variable capacitance 200 or phase-switched variable inductance 400) includes additional filtering components (not shown in FIGS. 2 and 4) to reduce harmonic content injected into the source and/or load (e.g., source 102 and load 114).

As described in regard to FIGS. 3 and 5, the phase-switched variable reactance (e.g., phase-switched variable capacitance 200 or phase-switched variable inductance 400), are half-wave switched, where the switch is operated so that the capacitor voltage (curve 306 of FIG. 3) and inductor current (curve 502 of FIG. 5) are unipolar. However, other switching schemes are also possible. For example, FIGS. 8 and 9 show illustrative waveforms of the current I and voltage V with respect to the switch control signal, Q, as a function of a cycle angle  $\theta$ , for the switched capacitor network shown in FIG. 3 and the switched inductor network shown in FIG. 5, respectively.

In particular, as shown in FIG. 8, curve 802 shows  $I(\theta)$ , curve **806** shows  $V_c(\theta)$  and curve **804** shows  $Q(\theta)$  for a full-wave switched capacitor. As shown in FIG. 9, curve 902 shows  $I_{I}(\theta)$ , curve **906** shows  $V(\theta)$  and curve **904** shows  $Q(\theta)$  for a full-wave switched inductor. When phaseswitched variable capacitance 200 is full-wave switched, the switch (e.g., switch 206) is turned off twice every cycle of  $I(\theta)$  (e.g.,  $Q(\theta)$  is zero), with the off periods being centered around the instants when the current  $I(\theta)$  is zero. For a purely sinusoidal excitation current  $I(\theta)$ , this results in a bipolar capacitor voltage waveform  $V_C(\theta)$ . Capacitor voltage  $V_C(\theta)$  has zero DC average value. Similarly, when phase-switched variable inductance 400 is full-wave switched, the switch (e.g., switch 406) is turned on twice every cycle of  $V(\theta)$  (e.g.,  $Q(\theta)$  has a logic high value), with the on periods being centered around the instants when the voltage  $V(\theta)$  is zero. For a purely sinusoidal excitation voltage  $V(\theta)$ , this results in a bipolar inductor current waveform  $I_L(\theta)$ , which also has zero DC average value. Thus, for a full-wave switched capacitor (or inductor), switch 206 is turned on and off twice per cycle of the RF signal from source 102 (e.g.,  $I(\theta)$  as shown by curve 802).

As with half-wave switching (e.g., as shown in FIGS. 3 and 5), the effective capacitance  $C_{EFF}$  and the effective inductance  $L_{EFF}$  at the switching frequency can be modulated by controlling the switching angle,  $\alpha$ , of the switch. The effective capacitance,  $C_{EFF}$ , of capacitor 204 can be represented as a function of a for a full-wave switched capacitor:

$$C_{EFF} = \frac{C_0 \cdot \pi}{2 \cdot [\pi - \alpha + \sin(\alpha) \cdot \cos(\alpha)]}$$

(2a)

Similarly, the effective inductance,  $L_{EFF}$ , of inductor **404** can be represented as a function of  $\alpha$ :

$$L_{EFF} = \frac{L_0 \cdot \pi}{2 \cdot [\pi - \alpha + \sin(\alpha) \cdot \cos(\alpha)]}. \tag{2b}$$

Thus, the effective capacitance/inductance that can be achieved for a given switching angle, a, with full-wave switched networks (e.g., relationships (2a) and (2b)) is half the effective capacitance/inductance that can be achieved with half-waved switched networks (e.g., relationships (1a) 5 and (1b)). However, full-wave switched networks inherently result in reduced harmonic content of the capacitor voltage and inductor current compared to half-wave switched networks for the same switching angle, a (i.e. the switching angle which controls the total switch conduction angle). On 10 the other hand, implementing full-wave switching requires the switch has to operate at twice the operating frequency (e.g., to switch twice per cycle). Further, for capacitive modulation, bidirectional blocking switches are required, which can complicate switch implementation with typical 15 semiconductor switches.

Relationships (1) and (2) above show that the effective capacitance and inductance for the switched networks shown in FIGS. 2 and 4 can be based upon the switching angle, α, for purely sinusoidal excitation signals. For exci- 20 tation signals that are not purely sinusoidal, the effective reactance can be controlled by appropriately selecting the timing or switching angle,  $\alpha$ , at which the switch turns off (or on) although relationships (1) and (2) cannot calculate an exact value of a. Together with the circuit waveforms that 25 determine zero-voltage (or zero current) points (for switch turn on (or off), switching angle  $\alpha$  determines the total conduction angle of the switch during the cycle. For excitation signals that are not purely sinusoidal, an adaptable look-up table (e.g., LUT 108), feedback circuit 110 or 30 feedforward circuit 104 (including optional digital predistortion circuit 107) might be employed to determine the required value of a for a given desired effective reactance.

Phase-switched variable capacitance 200 and phase-switched variable inductance 400 can be employed as building blocks for implementing phase-switched variable reactances and other adjustable circuits such as TMNs. Particularly, some applications could benefit substantially from variable reactances whose value can be controlled over a range spanning both capacitive and inductive reactances, 40 and/or by modulating the effective reactance over a more limited range. Augmenting phase-switched variable capacitance 200 and/or phase-switched variable inductance 400 with additional reactive components can provide a wider range of variable reactances.

FIGS. 10A-10D show illustrative embodiments of phase-switched reactance circuits that include both capacitive and inductive elements, thereby expanding a range over which the impedance of the phase-switched reactance circuit can be tuned as compared to the single-element circuits shown 50 in FIGS. 2 and 4.

For example, FIG. 10A shows phase-switched reactance circuit 1002 that includes inductor 1012 in series with phase-switched capacitor 1013. Phase-switched capacitor 1013 includes switch 1016 in parallel with capacitor 1014, 55 similarly as described in regard to FIG. 2. FIG. 10B shows phase-switched reactance circuit 1004 that includes inductor 1024 in series with capacitor 1022, with the series combination of inductor 1024 and capacitor 1022 arranged in parallel with phase-switched capacitor 1025. Capacitor 1022 60 is not phase-switched and, thus, is shown as  $C_{DC}$ . Phaseswitched capacitor 1025 includes switch 1028 in parallel with capacitor 1026, similarly as described in regard to FIG. 2. FIG. 10C shows phase-switched reactance circuit 1006 that includes capacitor 1032 in parallel with phase-switched inductor 1033. Phase-switched inductor 1033 includes switch 1036 in series with inductor 1034, similarly as

described in regard to FIG. 4. FIG. 10D shows phase-switched reactance circuit 1008 that includes inductor 1042 in parallel with capacitor 1044, with the parallel combination of inductor 1042 and capacitor 1044 arranged in series with phase-switched capacitor 1045. Inductor 1042 is not phase-switched and, thus, is shown as Loc. Phase-switched inductor 1045 includes switch 1048 in series with inductor 1046, similarly as described in regard to FIG. 4.

16

As would be understood by one of skill in the art, circuit variants other than the ones illustrated in FIGS. 10A-10D are also possible. For example, placing a capacitor in series with a phase-switched capacitor provides a net effective impedance having a maximum capacitance equal to the series combination of the capacitor and the physical capacitance of the phase-switched capacitor, and a minimum capacitance equal to the series combination of the capacitor and the phase-switched capacitance value.

As described in regard to FIGS. 6 and 7, a tradeoff exists for phase-switched variable capacitance 200 and phase-switched variable inductance 400 between their variable reactance range and the amount of harmonic content injected into the rest of the system. In other words, the range over which the effective reactance can be controlled is limited by the amount of harmonic content that can be tolerated within the system (e.g., by source 102 and/or load 114). Some embodiments might employ additional or external filtering components to reduce harmonic content injected to source 102 and/or load 114. However, in some embodiments, it might not be possible to employ additional filtering components.

Referring to FIGS. 11 and 12, in cases where additional filtering components are not employed, the harmonic content can be reduced by combining phase-switched variable capacitance 200 and phase-switched variable inductance 400 with one or more digitally controlled capacitor or inductor matrices that are not phase-switched. Such hybrid switched networks include an RF switch operated at the RF frequency of operation and with controlled phase and duty cycles with respect to the RF waveform. The hybrid switched network also includes digital switches associated with one or more capacitors or inductors in the switched matrix. The digital switches are typically operated at a much lower frequency than the RF frequency, but could be operated up to the RF frequency (e.g., on a cycle-by-cycle basis) determined by the control bandwidth of the effective reactance  $C_{EFF}$  or  $L_{EFF}$

Referring to FIG. 11, hybrid switched network 1100 includes a phase-switched reactance (e.g., capacitor  $C_0$  1116 and parallel switch 1118) and digitally controlled capacitor network 1102. Although shown as a phase-switched variable capacitance (e.g., capacitor  $C_0$  1116 and parallel switch 1118) coupled in parallel with digitally controlled capacitor network 1102 and load 114, in other embodiments, the phase-switched reactance might be implemented as a phase-switched variable inductance (e.g., such as shown in FIG. 4) coupled in series with digitally controlled capacitor network 1102 and load 114, or as one of the phase-switched reactance circuits shown in FIGS. 10A-D, or other equivalent circuits.

Digitally controlled capacitor network 1102 includes a plurality of capacitors and associated switches, shown as capacitors 1104, 1108, and 1112, and switches 1106, 1110, and 1114. In some embodiments, each of capacitors 1104, 1108, and 1112 have a unique capacitance value, allowing the capacitance value of digitally controlled capacitor network 1102 to be varied across a large capacitance range. For example, as shown in FIG. 11, capacitors 1104, 1108, and 1112 might increase from the phase-switched capacitor base

value (e.g.,  $C_0$ ) in increments of  $C_0$  until reaching a maximum capacitance value (e.g.,  $(2 \cdot 2^N - 1) \cdot C_0$ ), where N is the number of capacitors in digitally controlled capacitor network 1102).

Switches 1106, 1110, and 1114 are coupled in series with 5 corresponding ones of capacitors 1104, 1108, and 1112 and are operable to adjust the capacitance of digitally controlled capacitor network 1102 by connecting (or disconnecting) the respective capacitors. Switches 1106, 1110, and 1114 might operate based upon one or more control signals from control circuit 106. As described, switches 1106, 1110, and 1114 generally operate at a frequency less than the RF frequency to adjust the capacitance value of digitally controlled capacitor network 1102.

Referring to FIG. 12, hybrid switched network 1200 15 includes a phase-switched reactance (e.g., inductor  $L_0$  1216 and series switch 1218) and digitally controlled inductor network 1202. Although shown as a phase-switched variable inductance (e.g., inductor L<sub>0</sub> 1216 and series switch 1218) coupled in series with digitally controlled inductor network 20 1202 and in parallel with load 114, in other embodiments, the phase-switched reactance might be implemented as a phase-switched variable capacitance (e.g., such as shown in FIG. 2), or as one of the phase-switched reactance circuits shown in FIGS. 10A-D, or other equivalent circuits.

Digitally controlled inductor network 1202 includes a plurality of inductors and associated switches, shown as inductors 1206, 1210, and 1214, and switches 1204, 1208, and 1212. In some embodiments, each of inductors 1206, **1210**, and **1214** have a unique inductance value, allowing the inductance value of digitally controlled inductor network 1202 to be varied across a large inductance range. For example, as shown in FIG. 12, inductors 1206, 1210, and 1214 and 1218 might increase from the phase-switched reaching a maximum inductance value.

Switches 1204, 1208, and 1212 are coupled in parallel with corresponding ones of inductors 1206, 1210, and 1214 and are operable to adjust the inductance of digitally controlled inductor network 1202 by connecting (or shorting, 40 e.g., providing a low-impedance path to bypass the inductor) the respective inductors. Switches 1204, 1208, and 1212 might operate based upon one or more control signals from control circuit 106. As described, switches 1204, 1208, and 1212 generally operate at a frequency less than the RF 45 frequency to adjust the capacitance value of digitally controlled inductor network 1202.

Digitally controlled capacitor network 1102 and digitally controlled inductor network 1202 expand the range over which the reactance of the phase-switched reactance (e.g., 50 capacitor C<sub>0</sub> 1116 and parallel switch 1118, or inductor L<sub>0</sub> 1216 and series switch 1218) can be continuously varied without introducing excessive harmonic content to source 102 and/or load 114. For example, the embodiments shown in FIGS. 11 and 12 employ digitally controlled capacitor 55 network 1102 (or digitally controlled inductor network **1202**) to control the base value  $C_0$  (or  $L_0$ ) of the switched networks 1100 (or 1200). The switch of the phase-switched reactance (e.g., switch 1118 or switch 1218) can be operated to step-up the base capacitance Co (or inductance Lo) by a 60 factor determined by relationships (1) and (2) described above.

For example, the effective capacitance  $C_{EFF}$  at the switching frequency of hybrid switched capacitor network 1100 can be controlled between a lower capacitance value C<sub>0</sub> and an upper capacitance value by half-wave switching the RF switch with the switching angle,  $\alpha$ , varying from 0 to

18

approximately  $\pi/2$  as shown in FIG. 3. As shown in FIG. 7, RF switch operation with a switching angle,  $\alpha$ , less than  $\pi/2$ (90 degrees) corresponds to a peak harmonic distortion of less than approximately 35%. Thus, the hybrid switched networks (e.g., 1100 and 1200) allow continuous control of the effective reactance at the switching frequency over a wide capacitive (or inductive) range with minimum harmonic distortion and without the need for adjustable bias voltages or currents.