US008643347B2

# (12) United States Patent

### Giuliano et al.

#### (54) POWER CONVERTER WITH CAPACITIVE ENERGY TRANSFER AND FAST DYNAMIC RESPONSE

(75) Inventors: David M. Giuliano, Cambridge, MA

(US); David J. Perreault, Brookline,

MA (US); Robert C. N.

Pilawa-Podgurski, Cambridge, MA

(US)

(73) Assignee: Massachusetts Institute of Technology,

Cambridge, MA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/487,781

(22) Filed: Jun. 4, 2012

(65) **Prior Publication Data**

US 2012/0313602 A1 Dec. 13, 2012

#### Related U.S. Application Data

- (63) Continuation of application No. 12/427,599, filed on May 8, 2009, now Pat. No. 8,212,541.

- (60) Provisional application No. 61/051,476, filed on May 8, 2008.

- (51) Int. Cl. G05F 1/00

(2006.01)

(52) U.S. Cl.

USPC ...... **323/266**; 323/271

(58) Field of Classification Search

USPC ...... 323/266, 268, 271, 282 See application file for complete search history.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,513,364 | Α |   | 4/1985 | Nilssen        |         |

|-----------|---|---|--------|----------------|---------|

| 5 959 565 | Α | * | 9/1999 | Taniuchi et al | 341/172 |

## (10) Patent No.: US 8,643,347 B2

## (45) **Date of Patent:**

Feb. 4, 2014

| 6,198,645 | В1   | 3/2001  | Kotowski et al.  |  |  |

|-----------|------|---------|------------------|--|--|

| 6,515,612 |      | 2/2003  | Abel 341/172     |  |  |

| 6,563,235 | B1   | 5/2003  | McIntyre et al.  |  |  |

| 7,157,956 | B2 * | 1/2007  | Wei 327/337      |  |  |

| 7,375,992 | B2 * | 5/2008  | Mok et al 363/60 |  |  |

| 7,382,113 | B2   | 6/2008  | Wai et al.       |  |  |

| 7,633,778 | B2 * | 12/2009 | Mok et al 363/60 |  |  |

| 7,777,459 | B2 * | 8/2010  | Williams 323/266 |  |  |

| 7,812,579 | B2 * | 10/2010 | Williams 323/266 |  |  |

| 7,956,572 | B2   | 6/2011  | Zane et al.      |  |  |

| (C =t'1)  |      |         |                  |  |  |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

| DE | 103 58 299 A1 | 7/2005  |

|----|---------------|---------|

| EP | 0 513 920 A2  | 11/1992 |

| JP | 2002-62858    | 2/2002  |

## OTHER PUBLICATIONS

Axelrod, et al.; "Single-Switch Single-Stage Switched-Capacitor Buck Converter;" 4<sup>th</sup> Nordic Workshop on Power and Industrial Electronics; Jun. 2004; 5 pages.

#### (Continued)

Primary Examiner — Adolf Berhane

Assistant Examiner — Emily P Pham

(74) Attorney, Agent, or Firm — Daly, Crowley, Mofford & Durkee, LLP

#### (57) ABSTRACT

A converter circuit and related techniques for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. The circuits and techniques achieve high performance over a wide input voltage range or a wide output voltage range. The converter can be used, for example, to power logic devices in portable battery operated devices.

#### 8 Claims, 8 Drawing Sheets

## (56) References Cited

## OTHER PUBLICATIONS

## U.S. PATENT DOCUMENTS

| 8,000,117    | B2            | 8/2011  | Petricek         |

|--------------|---------------|---------|------------------|

| 8,085,524    | B2            | 12/2011 | Roozeboom et al. |

| 2004/0222775 | $\mathbf{A}1$ | 11/2004 | Muramatsu et al. |

| 2005/0213267 | A1            | 9/2005  | Azrai et al.     |

| 2007/0146020 | A1            | 6/2007  | Williams         |

| 2008/0013236 | $\mathbf{A}1$ | 1/2008  | Weng             |

| 2008/0157733 | A1            | 7/2008  | Williams         |

| 2008/0158915 | A1            | 7/2008  | Williams         |

| 2009/0072800 | A1            | 3/2009  | Ramadass et al.  |

| 2010/0117612 | A1            | 5/2010  | Klootwijk et al. |

Giuliano, et al.; "Architectures and Topologies for Power Delivery;" Biannual Review of MIT Center for Integrated Circuits; Power Point Presentation; May 9, 2007; 17 slides.

Sun, et al.: "High Power Density High Efficiency System Two-Stage

Sun, et al.; "High Power Density, High Efficiency System Two-Stage Power Architecture for Laptop Computers;"  $37^{th}$  IEEE Power Electronics Specialists Conference apros; 06; Jun. 18, 2006; 7 pages. Image File Wrapper downloaded on Jun. 4, 2012 for U.S. Appl. No. 12/437,599, filed May 8, 2009; 207 pages.

<sup>\*</sup> cited by examiner

PRIOR ART

PRIOR ART

r DI

### POWER CONVERTER WITH CAPACITIVE ENERGY TRANSFER AND FAST DYNAMIC RESPONSE

## CROSS REFERENCE TO RELATED APPLICATION

This application is a continuation of co-pending U.S. application Ser. No. 12/437,599 filed May 8, 2009 which claims the benefit of U.S. Provisional Application No. 61/051,476 filed May 8, 2008 under 35 U.S.C. §119(e) which application is hereby incorporated herein by reference in its entirety.

## STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH

This invention was made with government support under Contract No. SC001-0000000124 was awarded by the Department of Defense. The government has certain rights in this invention.

#### FIELD OF THE INVENTION

The circuits and techniques described herein relate generally to power converters and more particularly to power converters having a capacitive energy transfer and a fast dynamic response.

#### BACKGROUND OF THE INVENTION

The advent of portable electronics and low-voltage digital circuitry has resulted in a need for improved DC-DC converters. DC-DC converters that can provide a low voltage output (<2 V) regulated at high bandwidth, while drawing energy from a higher, wide-ranging input voltage (e.g., typically 35 about a 2:1 range) are particularly useful for supplying battery-powered portable electronics. The size, cost, and performance advantages of integration make it desirable to integrate as much of the DC-DC converter as possible, including control circuits, power switches, and even passive components. 40 Moreover, it is often desirable, if possible, to integrate the power converter or portions thereof with the load electronics.

One common approach is the use of a switched-mode power converter in which energy is transferred from the converter input to output with the help of intermediate energy 45 storage in the magnetic field of an inductor or transformer. Such magnetics based designs include synchronous buck converters, interleaved synchronous buck converters, and three-level buck converters. Designs of this type can efficiently provide a regulated output from a variable input voltage with high-bandwidth control of the output.

For magnetics-based designs operating at low, narrowrange input voltages, it is possible to achieve extremely high switching frequencies (up to hundreds of Megahertz), along with correspondingly high control bandwidths and small pas- 55 sive components (e.g., inductors and capacitors). It also becomes possible to integrate portions of the converter with a microprocessor load in some cases. These opportunities arise from the ability to use fast, low-voltage, process-compatible transistors in the power converter. At higher input voltages and wider input voltage ranges, much lower switching frequencies (on the order of a few MHz and below) are the norm, due to the need to use slow extended-voltage transistors (on die) or discrete high-voltage transistors. This results in much lower control bandwidth, and large, bulky passive components (especially magnetics) which are not suitable for integration or co-packaging with the devices.

2

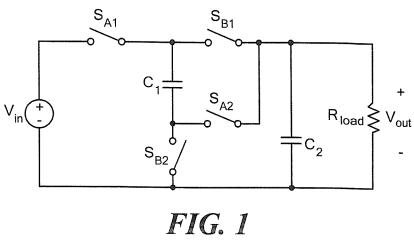

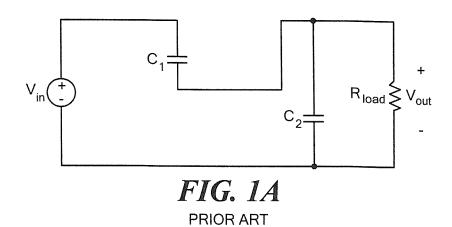

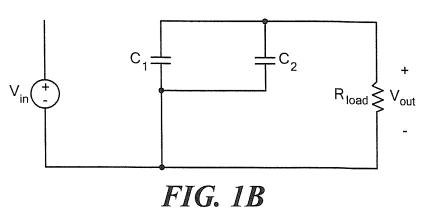

Another conversion approach that has received a lot of attention for low-voltage electronics is the use of switchedcapacitor (SC) based DC-DC converters. This family of converters is well-suited for integration and/or co-packaging passive components with semiconductor devices, because they do not require any magnetic devices (inductors or transformers). An SC circuit includes of a network of switches and capacitors, where the switches are turned on and off periodically to cycle the network through different topological states. Depending upon the topology of the network and the number of switches and capacitors, efficient step-up or stepdown power conversion can be achieved at different conversion ratios. An example of a step-down SC topology is shown in FIG. 1, which has an ideal conversion ratio  $M=V_o/V_i=2$ . When switches  $S_{A1}$  and  $S_{A2}$  are closed, the capacitors are charged in series as illustrated in FIG. 1A, and when switches  $S_{B1}$  and  $S_{B2}$  are closed, the capacitors are discharged in parallel as illustrated in FIG. 1B.

SC DC-DC converters have been described in prior art <sup>20</sup> literature for various conversion ratios and applications, and the technology has been commercialized. These types of converters have found widespread use in low-power battery-operated applications, thanks to their small physical size and excellent light-load operation.

There are, however, certain limitations of the switched-capacitor DC-DC converters that have prohibited their wide-spread use. Chief among these is the relatively poor output voltage regulation in the presence of varying input voltage or load. The efficiency of switched capacitor converters drops quickly as the conversion ratio moves away from the ideal (rational) ratio of a given topology and operating mode. In fact, in many topologies the output voltage can only be regulated for a narrow range of input voltages while maintaining an acceptable conversion. Another disadvantage of early SC converters is discontinuous input current which has been addressed in some prior art approaches. These new techniques, however, still suffer from the same degradation of efficiency with improved regulation as previous designs.

One means that has been used to partially address the limitations of switched-capacitor converters is to cascade a switched capacitor converter having a fixed step-down ratio with a linear regulator or with a low-frequency switching power converter having a wide input voltage range to provide efficient regulation of the output. Another approach that has been employed is to use a switched-capacitor topology that can provide efficient conversion for multiple specific conversion ratios (under different operating modes) and select the operating mode that gives the output voltage that is closest to the desired voltage for any given input voltage. None of these approaches, however, are entirely satisfactory in achieving the desired levels of performance and integration.

A challenge, then, is to achieve the small size and ease of integration often associated with SC-based power converters while maintaining the high-bandwidth output regulation and high efficiency over a wide input voltage range associated with magnetics-based designs.

#### SUMMARY OF THE INVENTION

A converter circuit and related technique for providing high power density power conversion includes a reconfigurable switched capacitor transformation stage coupled to a magnetic converter (or regulation) stage. One objective of the circuits and techniques described herein is to provide high power density power conversion circuits which convert an input voltage to an output voltage. In some cases, the circuit converts input voltages to output voltages which are lower

than the input voltages and with a fast transient response. In some cases, the circuits and techniques can achieve high performance over a relatively wide input voltage range. This type of converter can be used to power logic devices in portable battery operated applications, for example, which often sexperience wide input voltage ranges. In other cases it may be desirable to operate the power converter circuit so as to provide a relatively wide range of output voltages. This type of converter could be used to power digital circuits with dynamic voltage scaling, or for supplying power to polar RF power amplifiers, for example, where wide output voltage ranges are commonly required.

Conventional (e.g. magnetic-based) power converters must typically employ semiconductor switches that are rated for voltages similar in size to the input voltage. These relatively 15 high-voltage blocking devices are inherently slower than lower-voltage devices, and suffer from a higher on-state resistance or larger gate capacitance which both reduce overall efficiency. It would thus be desirable to have a converter that provides high efficiency and fast regulation of the output over a wide input voltage range. Such a converter that combines the strengths of the SC techniques (ease of integration, lightload performance) with the high efficiency and good regulation of conventional switched-mode power converters would be a significant improvement over conventional designs.

In accordance with the circuits and techniques described herein, a power converter circuit includes a reconfigurable switched capacitor transformation stage adapted to accept an input voltage at input terminals thereof and provide power conversion at multiple distinct conversion ratios and provide an intermediate output voltage (or more simply, an intermediate voltage) at output terminals thereof wherein the transformation stage is controlled as a function of input voltage such that the intermediate voltage is smaller than the input voltage and varies over a much smaller range (ratio) than the input voltage. The power converter circuit further includes a regulation stage coupled to receive the intermediate output voltage provided by the reconfigurable switched capacitor transformation stage and to provide an output voltage at a pair of regulation stage output terminals.

With this particular arrangement, a reconfigurable switched capacitor converter which can provide efficient power conversion at multiple distinct conversion ratios is provided. By providing the transformation stage as a reconfigurable switched capacitor converter with multiple transfor- 45 mation ratios, the intermediate voltage provided to the regulation stage is smaller than the input voltage and varies over a much smaller range (ratio) than the input voltage. Thus, the regulation stage may operate as a low voltage regulation stage capable of relatively high switching frequencies. Thus a converter able to accept a relatively large input voltage range and provide a relatively large output current range is provided. The transformation stage provides power conversion at multiple distinct conversion (or transformation) ratios as a function of input voltage. For example, the conversion ratio of the 55 transformation stage may be selected from among the allowed set of conversion ratios to keep the intermediate voltage as close to a desired reference voltage or as large as possible below some specified voltage. In some cases, the transformation ratio of the transformation stage may also be 60 selected based on a desired or actual system output voltage. For example, the reference voltage for the intermediate voltage (at the output of the transformation stage) may be set based on the desired output system voltage. In these designs, the conversion (i.e. the transformation) ratios are provided as 65 a function of input voltage such that an intermediate voltage provided at an output of the transformation stage varies over

4

a range of voltages which is smaller (ratio) than the range of voltages over which the input voltage varies.

In another aspect of the concepts described herein, by providing the transformation stage as a reconfigurable switched capacitor converter with multiple transformation ratios, the converter can better supply a range of output voltages while maintaining high-efficiency operation. In some cases, the range of output voltages may be narrower than the input voltage range while in other cases the range of output voltages may be wider than the input voltage range. The transformation stage provides power conversion at multiple distinct conversion (or transformation) ratios as a function of the desired or actual output voltage. For example, the conversion ratio of the transformation stage may be selected from among an allowed or available set of conversion ratios to maintain an intermediate voltage (e.g. a voltage or range of voltages provided at the output of the transformation stage and at the input of the regulation stage) as close to a desired factor more than the output voltage (e.g., twice the desired output voltage) while not having the intermediate voltage exceed an allowed voltage limit or range on the input of the regulation stage. In this manner, the regulation stage can operate over a voltage conversion ratio range that is narrower than the range over which the desired output voltage varies, enabling better design of the regulation stage. In some cases, the transformation ratio of the transformation stage may also be selected based upon the system input voltage. In these designs, the conversion (i.e. the transformation) ratios of the transformation stage are provided as a function of the output voltage or output voltage reference such that an intermediate voltage provided at an output of the transformation stage varies over a range of voltages which is smaller (ratio) than the range of voltages over which the desired output voltage varies. Thus, while the circuit architecture described herein can be used in applications where it is necessary to handle a wide-range-input voltage, the circuit architecture described herein is also valuable for handling wide-range-outputs. 40 Modern digital electronics often operate dynamically over a range of output voltages, and thus it may be desirable to provide a single converter to handle a range of desired output voltages.

Thus, a controller for providing control signals to switches in one or both transformation and regulation stages can utilize either or all of an input voltage, an output voltage and an intermediate voltage to determine what control signals to provide to switching elements within transformation or regulation stages and thus control the operation of the transformation and regulation stages.

In another aspect, the transformation stage and regulation stage each include two or more switches. The switches in the regulation stage are selected to operate at a switching frequency which is higher than the switching frequency of the switches in said transformation stage. This benefits the efficiency, power density and control bandwidth of the converter. For a given switching frequency at small size scales, the power density of a switched capacitor converter can be much higher than that of a magnetic converter. Moreover, a (lowvoltage) magnetic converter stage can be efficiently switched at a much higher frequency than a (high-voltage) switched capacitor converter stage. Thus, operating the SC transformation stage at low frequency and operating the magnetic regulation stage at high frequency provides the best combination of system efficiency and power density. Moreover, as the switching frequency of the regulation stage sets the overall control bandwidth, increased frequency of the regulation

stage as compared to the transformation stage enables provision of fast transient performance while maintaining high efficiency

In accordance with a further aspect of the circuits and techniques described herein, a power converter circuit 5 includes a switched capacitor circuit coupled to an auxiliary high-frequency converter wherein the high-frequency switching converter switches at a switching frequency higher than that of said switched-capacitor circuit and recovers energy normally dissipated when charging capacitors of said 10 switched capacitor circuit.

With this particular arrangement, a switched capacitor converter which can provide efficient power conversion at is provided. This switched capacitor converter may provide efficient conversion at one conversion ratio or in other designs at 15 multiple distinct conversion ratios. The high-frequency switching converter runs at a switching frequency far higher than that of the switched-capacitor circuit and recovers the energy that is normally dissipated when charging and/or discharging the capacitors. The high-frequency switched con- 20 verter can also provide high-bandwidth regulation of the converter system output. The circuit can be configured such that the difference between the input voltage and the sum of the charging capacitor voltages appears across the input terminals of the fast switching converter. Because this voltage is 25 substantially lower than the switched-capacitor circuit input voltage, the auxiliary regulating converter can utilize fast, low-breakdown semiconductor switches that enable fast operation and regulation. By making the apparent input resistance of the auxiliary converter higher than the ESR of the 30 switched-capacitor and the SC circuit semiconductor switch resistances, a majority of the capacitor-charging energy can be recovered. Both of these embodiments allow for a sub 1 V dc output with high-bandwidth control of the output.

Thus, described herein are two embodiments, each of 35 which takes advantage of both switched capacitor and magnetics-based switching regulator technology. The first embodiment combines a high efficiency reconfigurable switched capacitor transformation stage with a high frequency, low-voltage regulation stage. This type of architec- 40 ture will achieve its highest integration when implemented in a multiple voltage monolithic process, such as an extended drain process. The devices in the switched capacitor network need not block the full supply voltage, and depending upon the configuration, they need to block different fractions of the 45 supply voltage. Similarly, high speed low voltage devices can be used in the switching regulator since it only sees a voltage slightly above the output voltage. Thus, the efficiency of the full converter can be optimized by using different voltage devices.

The second embodiment tightly couples a switched capacitor circuit with an auxiliary high-frequency converter (e.g. a low-voltage magnetics based converter). The high-frequency switching converter runs at a switching frequency far higher than that of the switched-capacitor circuit and recovers the 55 energy that is normally dissipated in parasitic resistances when charging and/or discharging the capacitors. The highfrequency switched converter can also provide high-bandwidth regulation of the converter system output. The circuit can be configured such that the difference between the input 60 voltage and the sum of the charging capacitor voltages appears across the input terminals of the fast switching converter. Because this voltage is substantially lower than the switched-capacitor circuit input voltage, the auxiliary regulating converter can utilize fast, low-breakdown semiconduc- 65 tor switches that enable fast operation and regulation. By making the apparent input resistance of the auxiliary con6

verter higher than the equivalent series resistance (ESR) of the switched-capacitor and the SC circuit semiconductor switch resistances, a majority of the energy usually lost in capacitor-charging can be recovered. Both of these embodiments allow for a sub 1 V dc output with high-bandwidth control of the output.

In accordance with a still further aspect of the concepts described herein, an integrated CMOS circuit includes a reconfigurable switched capacitor transformation stage having a transformation stage input port and a transformation stage output port and comprising one or more CMOS switches and one or more discrete or integrated storage elements, said transformation stage configured to accept an input voltage at the transformation stage input port and provide an intermediate voltage at the transformation stage output port; and a regulation stage having a regulation stage input port and a regulation stage output port and comprising one or more CMOS switches implemented as base transistors of a CMOS process and one or more discrete or integrated storage elements, said regulation stage configured to accept the intermediate voltage provided by said reconfigurable switched capacitor transformation stage and configured to provide an output voltage at the regulation stage output port. In a preferred embodiment, the switches in said CMOS reconfigurable switched capacitor transformation stage and said CMOS regulation stage are provided in a single CMOS process. It should be appreciated that in some embodiments, storage elements (e.g. capacitors) in one or both of the reconfigurable switched capacitor transformation stage and/or the regulation stage may not be integrated onto the integrated circuit while in other embodiments, the storage elements in one or both of the reconfigurable switched capacitor transformation stage and the regulation stage may be integrated onto the integrated circuit along with the switches.

In accordance with a still further aspect of the concepts described herein a power converter circuit includes a switched capacitor circuit having a switched-capacitor input port and a switched capacitor output port, said switched-capacitor circuit comprising a plurality of switches and one or more capacitors, said switched-capacitor circuit switching the capacitors between at least two states to transfer energy from the switched-capacitor input port to the switched-capacitor output port, and an auxiliary converter stage coupled to said switched capacitor circuit wherein said auxiliary converter stage switches at a switching frequency higher than that of said switched-capacitor circuit such that said auxiliary converter recovers energy normally dissipated when charging or discharging capacitors of said switched capacitor circuit.

In one embodiment, the auxiliary converter recovers energy normally dissipated when charging capacitors in said switched capacitor circuit by absorbing an instantaneous difference between stacked capacitor voltages in said switched capacitor circuit and an input voltage or an output voltage of the power converter circuit.

In one embodiment, the auxiliary converter stage comprises a plurality of switches, and one or more magnetic energy storage components and the regulation stage switches at a frequency which is at least five times that of the switching frequency of the switched capacitor circuit.

In one embodiment, the switched capacitor circuit and said auxiliary circuits are provided as CMOS circuits. In a preferred embodiment, the switches in the CMOS switched capacitor circuit and CMOS auxiliary circuits are provided in a single integrated process. In a preferred embodiment, the

switches in the CMOS auxiliary circuits are implemented with base transistors of a CMOS process.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing features of the circuits and techniques described herein, may be more fully understood from the following description of the drawings in which:

FIG. 1 is a schematic diagram of a prior art switched-capacitor circuit;

FIG. 1A is a schematic diagram of a prior art switchedcapacitor circuit in a first state with capacitors charging in series:

FIG. 1B is a schematic diagram of a prior art switchedcapacitor circuit in a second state with capacitors discharging in parallel;

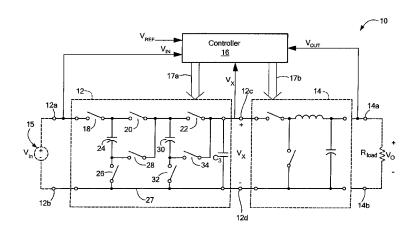

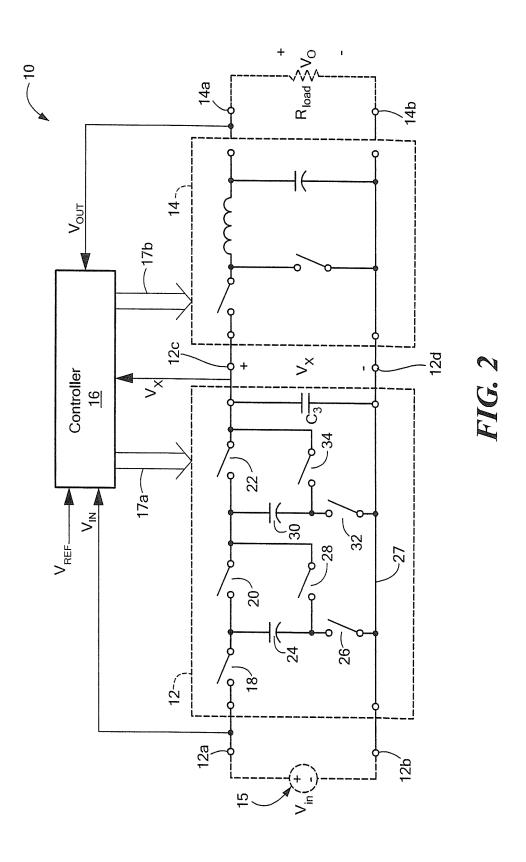

FIG. 2 is a block diagram of a converter having a transformation stage and a regulation stage;

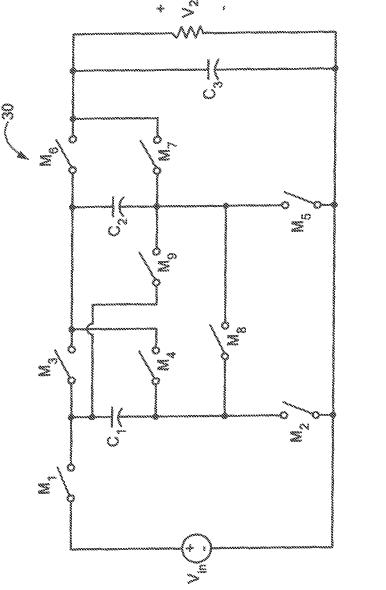

FIG. 3 is a schematic diagram of a reconfigurable switched-capacitor converter having a plurality of capacitors;  $^{20}$

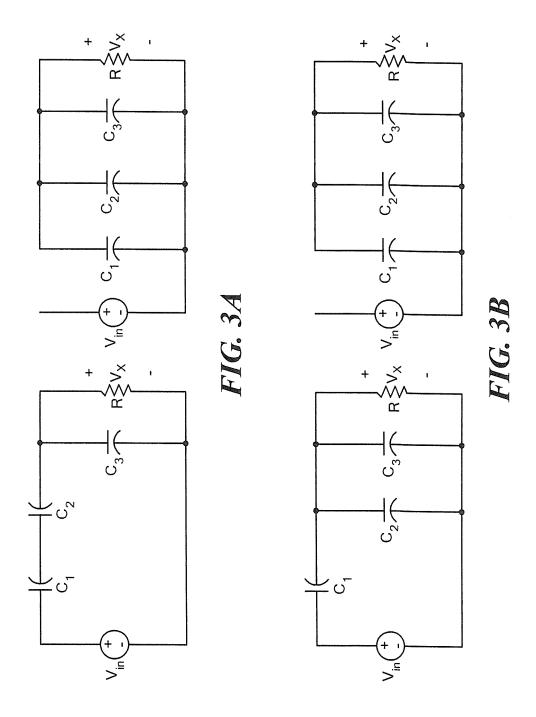

FIG. 3A is a schematic diagram of a switched-capacitor circuit operating at a conversion ratio of one-third (1/3);

FIG. 3B is a schematic diagram of a switched-capacitor circuit operating at a conversion ratio of one-half  $(\frac{1}{2})$ ;

FIG. 3C is a schematic diagram of a switched-capacitor <sup>25</sup> circuit operating at a conversion ratio of two-thirds (<sup>2</sup>/<sub>3</sub>);

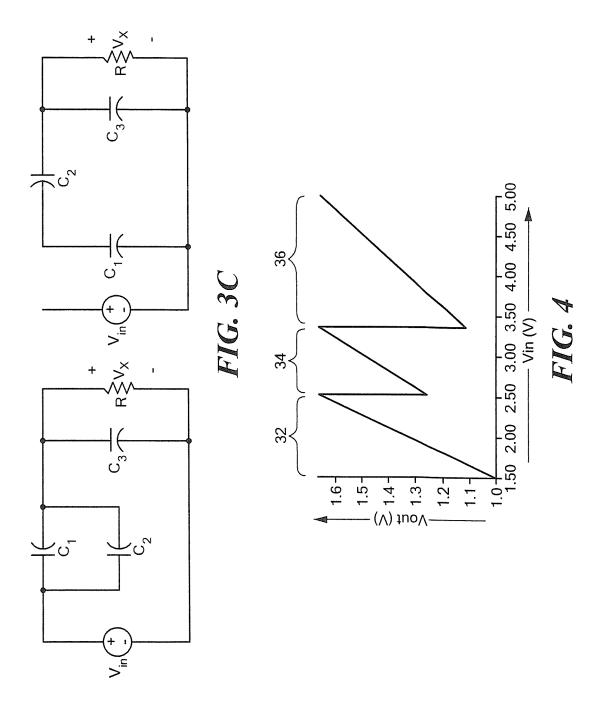

FIG. 4 is a plot of output voltage vs. input voltage of an SC converter having three distinct step-down ratios (1/3, 1/2, 2/3) and a predetermined maximum output voltage;

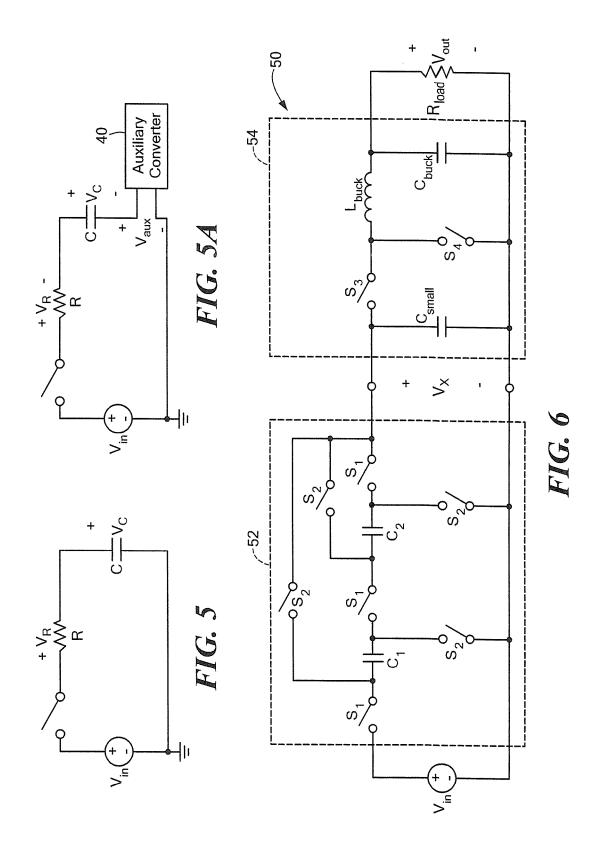

FIG.  $\bf 5$  is a schematic diagram illustrating charging of a  $^{30}$  capacitor with resistive power loss;

FIG. 5A is a schematic diagram illustrating charging of a capacitor with energy recovery by auxiliary converter;

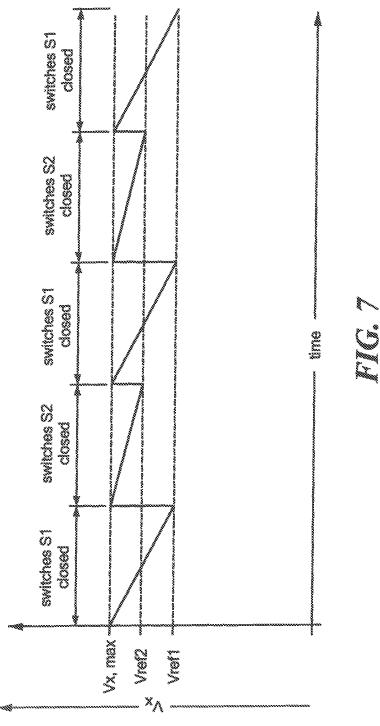

FIG. 6 is a schematic diagram of a power converter circuit which includes a switched-capacitor converter stage coupled 35 to a regulating converter stage;

FIG. 7 is a plot of switch configuration vs. voltage; and

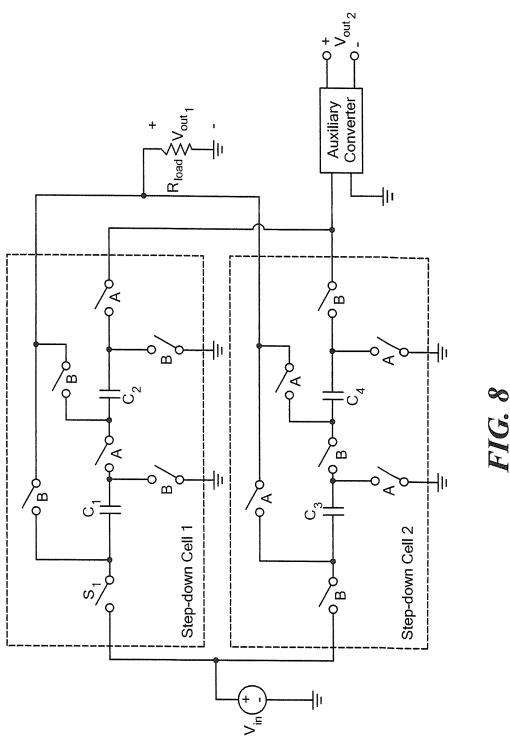

FIG. **8** is a schematic diagram of a power converter circuit which includes a switched-capacitor converter stage coupled to a regulating auxiliary converter stage which provides a 40 separate output voltage.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Before describing several exemplary embodiments of power converter circuits and processing performed by and on such power converter circuits, it should be appreciated that, in an effort to promote clarity in explaining the concepts, reference is sometimes made herein to specific switched capacitor 50 circuits or specific switched capacitor circuit topologies. It should be understood that such references are merely exemplary and should not be construed as limiting. After reading the description provided herein, one of ordinary skill in the art will understand how to apply the concepts described herein to 55 provide specific switched capacitor (SC) circuits or specific switched capacitor circuit topologies. For example, while series-parallel SC topologies may be disclosed herein, such disclosure is provided to promote clarity in the description of the general concepts described herein. After reading the disclosure provided herein those of ordinary skill in the art will appreciate that a series-parallel SC topology is only one of many possible topologies. It should thus be understood that although specific switched capacitor circuits or specific switched capacitor circuit topologies are not specifically disclosed herein, such circuits still fall within the scope of the concepts claimed herein.

8

It should be appreciated that reference is also sometimes made herein to particular input, output and/or intermediate voltages and/or voltage ranges as well as to particular transformation values and or ranges of transformation values. It should be understood that such references are merely exemplary and should not be construed as limiting.

Reference is also sometimes made herein to particular applications. Such references are intended merely as exemplary should not be taken as limiting the concepts described herein to that particular application.

Reference is also sometimes made herein to circuits having switches or capacitors. Its should be appreciated that any switching elements or storage elements having appropriate electrical characteristics (e.g. appropriate switching or storage characteristics) may, of course, also be used.

Thus, although the description provided herein below explains the inventive concepts in the context of a particular circuit or a particular application or a particular voltage or voltage range, those of ordinary skill in the art will appreciate that the concepts equally apply to other circuits or applications or voltages or voltage ranges.

Referring now to FIG. 2, a power converter circuit 10 includes a first stage 12 (also referred to as a "reconfigurable switched capacitor transformation stage" or a "switched capacitor stage" or more simply a "transformation stage") and a second stage 14 (also referred to as switching converter regulation stage or more simply a "regulation stage"). A voltage source 15 (here shown in phantom since it is not properly a part of the power converter circuit 10) is coupled between a pair of input terminals 12a, 12b of the transformation stage of power converter circuit 10 and a load R<sub>L</sub> (also shown in phantom since it is not properly a part of the power converter circuit 10) coupled to output terminals 14a, 14b of regulation stage 14 and across which is generated an output voltage  $V_O$ . A controller circuit 16 is coupled to receive a reference voltage  $V_{REF}$ , as well as some or all of the input and output voltages  $\mathbf{V}_{I\!N}$  and/or  $\mathbf{V}_{OUT}$  and an intermediate output voltage  $V_x$  (or more simply, intermediate voltage  $V_x$ ). Controller 16 receives signals provided thereto (e.g. any or all of  $V_{IN}$ ,  $V_{OUT}$ and/or intermediate voltage V<sub>x</sub>) and in response thereto (and in accordance with a desired operating mode) provides control signals on paths 17a, 17b to either or both of the transformation and regulation stages 12, 14, respectively.

Transformation stage 12 receives the input voltage (e.g.  $V_{I\!N^*}$ ) and operates to provide a transformed or intermediate voltage  $V_X$  at terminals 12C-12D. Thus transformed voltage  $V_X$  is provided to input terminals of regulation stage 14.

It should be appreciated that the input voltage  $V_{IN}$  may vary over a relatively wide voltage range. The particular voltage range over which the input voltage may vary depends upon the particular application. For example, in some applications the range of input voltages may be from about 1.5 volts (V) to about 5.0V. In other applications the range of input voltages may be from about 6V to about 12V. In still other applications the input voltage range may be from about 10V to about 14V. For example, in a converter circuit for battery-powered portable electronics applications, operation may be typically be required across an input voltage range from 2.4 V to 5.5 V.

Regardless of the input voltage, however, the transformation stage 12, maintains transformed voltage  $V_X$  over a voltage range which is relatively narrow compared with the input voltage range. For example, in the case where the input voltage range is from about 1.5 volts (V) to about 5.0V, the output voltage of the transformation stage 12 may range from about 1.0V to about 1.66V. Furthermore, the transformation ratios utilized by the transformation stage 12 are selected as a function of the input voltage  $V_{IN}$ . For example, the conversion

ratio of the transformation stage may be dynamically selected from among the allowed set of conversion ratios such that the intermediate voltage V<sub>x</sub> will be as large as possible while remaining below a specified maximum voltage. Thus, by adjusting a transformation ratio, transformation stage 12 can 5 accept a wide range of input voltages while maintaining the transformed voltage over a voltage range which is relatively narrow compared with the input voltage range. For example, consider a transformation stage with an input voltage range of 1.5 to 5.0 V and having allowed conversion ratios of 1/3, 1/2, 10 and <sup>2</sup>/<sub>3</sub>. It is possible to meet a goal of maximizing an intermediate voltage while at the same time keeping it below a specified maximum of approximately 1.66 V by operating at a conversion ratio of <sup>2</sup>/<sub>3</sub> for input voltages from 1.5 V to 2.5 V, operating at a conversion ratio of one half for input voltages 15 from 2.5 V to 3.33 V, and operating at a conversion ratio of 1/3 for input voltages from 3.33 V to 5 V.

The transformation stage 12 and regulation stage 14 each include one or more switch components and one or more energy storage components. The components which provide 20 the transformation stage 12 are selected such that the transformation stage has a switching frequency which is relatively low compared with the switching frequency of the regulation stage. Thus, the transformation stage may be referred to a low frequency stage while the regulation stage may be referred to 25 as a high frequency, low voltage magnetic stage. The difference in switching speeds of the transformation stage and regulation stage switches (i.e. the frequency separation between the switching frequencies of the switches) is selected based upon a variety of factors including but not limited to the 30 gating and switching loss characteristics of the switches It should, of course, be appreciated that a tradeoff must be made between switching frequency and the voltage levels (and/or range of voltages) which must be accepted by and provided by the transformation and regulation stages.

Transformation stage 12 includes a first plurality of coupled switches 18, 20, 22 coupled between terminal 12a and a terminal 12c.

A first capacitor 24 has a first terminal coupled to a first terminal of a switch 26. A second terminal of switch 26 is coupled to an interconnect path 27 coupled between terminal 12b and a terminal 12d. In this particular embodiment, interconnect path 27 is coupled to a negative terminal of the voltage source 16.

A first terminal of a switch 28 is coupled to the second terminal of capacitor 24 and a second terminal of switch 28 is coupled to a node between switches 20 and 22.

A second capacitor 30 has a first terminal coupled to a first terminal of switch 22 and a second terminal coupled to a first 50 terminal of a switch 32. A second terminal of switch 32 is coupled to the interconnect path coupled between terminal 12b and terminal 12d.

A first terminal of a switch 34 is coupled to the second terminal of capacitor 30 and a second terminal of switch 34 is 55 coupled to a second terminal of switch 22. Thus, by proper operation of switches 18, 20, 22, 26, 28, 32 and 34, capacitors 24 and 30 may be selectively coupled in parallel between terminals 12c and 12d. Alternatively, by proper operation of switches 18, 20, 22, 26, 28, 32 and 34, capacitors 24 and 30 60 may be selectively coupled in parallel with switches 20, 22, respectively, creating a series stack between terminal 12a and terminal 12c.

It should, of course, be appreciated that the above-described operating mode is merely one of a plurality of differ- 65 ent possible operating modes in a reconfigurable circuit. Another exemplary operating mode (or circuit configuration)

10

is illustrated in FIG. 3B. The system dynamically selects between a plurality of possible patterns and thus is said to be dynamically reconfigurable.

The transformation stage 12 corresponds to a reconfigurable switched capacitor converter. By appropriately selecting the switching patterns of the switches from among the possible patterns, the switched capacitor converter is reconfigurable and thus is able to provide efficient power conversion at multiple distinct conversion ratios. The operating mode of the transformation stage 12 is controlled as a function of input voltage. For example, for large input voltages one can operate the circuit to follow the switching patterns in FIG. 3A, providing 3:1 conversion, while for lower input voltages one can operate the circuit to follow the switching patterns of FIG. 3b, thus providing 2:1 conversion. In this way, transformation stage 12 can efficiently provide an intermediate voltage  $V_r$  between terminals 12c, 12d that is smaller than the input voltage  $V_{IN}$  and which varies over a much smaller range (ratio) than the input voltage  $V_{IN}$ .

The second, or regulating, stage 14 corresponds to a magnetic-based switching power converter which operates from the low, narrow-range (i.e. any range less than the input voltage range; for example, if the ratio of  $V_{IN}/V_{O}$  equals 2:1 then anything less than that would be considered narrow-range) intermediate voltage to regulate the output voltage V<sub>o</sub>. As this stage operates from a relatively low, narrow input voltage range, it can be designed to operate at relatively high frequencies. Since component size is related to switching frequency (e.g. the higher the switching frequency, the smaller the component), the circuit may be implemented using passive components which are relatively small in size and which provide high-bandwidth regulation of the output. Thus, power converter 10 converts power in two stages (i.e. the transformation stage 12 and the regulating stage 14) and together, the two stages can provide very small size, high efficiency, and high control bandwidth characteristics.

The transformation or switched-capacitor stage 12 is terminal of switch 18 and a second terminal coupled to a first 40 designed (e.g. by inclusion of multiple switched capacitor building blocks) to efficiently convert power at multiple distinct voltage conversion ratios. The number of capacitors in the converter stage determines both the maximum conversion ratio and the total possible number of distinct conversion ratios. It should thus be appreciated that the particular number of switches and capacitors included in the transformation stage depends upon a variety of factors including but not limited to the input voltage range for a particular application and the output voltage required for a particular application, and how many different transformation ratios are desired to reduce the intermediate voltage range.

> The power converter circuit described herein may be fabricated as an integrated circuit using a CMOS process. In this case, an integrated CMOS circuit includes a reconfigurable switched capacitor transformation stage provided from one or more CMOS switches and one or more storage elements, in which the storage elements may be realized as either integrated capacitors or external devices. The regulation stage would also be provided from one or more CMOS switches implemented and one or more storage elements. Again, the storage elements may be integrated, discrete, or provided as bond wires. In a preferred embodiment, the switches in said CMOS reconfigurable switched capacitor transformation stage and said CMOS regulation stage are fabricated in a single CMOS process. In the case where it is desirable for the switches of the regulation stage to switch at a higher frequency (in some cases a significantly higher frequency) than

the switches in the transformation stage, the switches of the regulation stage may be fabricated as base transistors in the CMOS process.

Referring now to FIGS. **3-3**C in which like elements are provided having like reference designations, a transformation 5 stage **30** (also referred to as a switched capacitor stage) includes eight switches M1-M8 and three capacitors C1-C3. The switches may be selectively opened and closed as shown in Table 1 below to provide three distinct conversion ratios (in this case, step-down ratios) of: ½; ½; and ½.

12

Referring now to FIG. 4, one possible windowing scheme for transformation stage 30 (a/k/a switched capacitor stage 30) of FIG. 3 is shown. Transformation stage 30 can accept an input voltage in the range of about 1.5V to about 5.0V (3.33: 1) and convert it into window of about 0.66 V ranging from about 1V to about 1.66V. Various control schemes can be used to accomplish this task. That is, the particular manner in which switches in transformation stage 30 (FIG. 3) are selectively opened and closed to provided a desired transformation ratio may be selected based upon a variety of factors includ-

TABLE 1

| $V_2/V_1$         | $M_1$             | $M_2$             | $M_3$             | $M_4$             | $M_5$            | $M_6$            | $M_7$             | M <sub>8</sub>    | $M_9$             |

|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|-------------------|-------------------|-------------------|

| 1/3<br>1/2<br>2/3 | clk<br>clk<br>clk | clk<br>clk<br>clk | clk<br>clk<br>clk | clk<br>clk<br>off | clk<br>on<br>off | clk<br>on<br>clk | clk<br>off<br>clk | off<br>off<br>clk | off<br>off<br>clk |

| $V_{max}$         | $\frac{2}{3}V_1$  | $\frac{2}{3}V_1$  | $\frac{1}{2}V_1$  | $\frac{1}{2}V_1$  | $\frac{2}{3}V_1$ | $\frac{1}{3}V_1$ | $\frac{1}{2}V_1$  | $\frac{1}{2}V_1$  | $\frac{1}{2}V_1$  |

The SC transformation stage is provided with a digital clock signal clk. A second signal /clk is also generated, which may simply be the complement of clk (i.e., is high when clk is low and low when clk is high), or which may be generated as a non-overlapping complement as is well known in the art. The elements of the first three rows of table 1 indicate the switching states of the individual switches as the circuit is clocked. Each row shows operation for a different conversion ratio (i.e., operating configuration). An entry clk indicates that the switch is on (closed) when clk is asserted and off (open) otherwise, an entry /clk indicates that the switch is on when the complementary signal /clk is asserted and off otherwise, an entry off indicates that the switch is always off for that conversion ratio, and an entry on indicates that a switch is always on for that conversion ratio.

Referring now to FIG. 3A, with a switching pattern set in accordance with the second row of Table 1, the switched-capacitor circuit 30 provides a step down ratio of one-third  $^{40}$  ( $^{1}$ /<sub>3</sub>).

Referring now to FIG. 3B, with a switching pattern set in accordance with the third row of Table 1, the switched-capacitor circuit 30 provides a step down ratio of one-half  $(\frac{1}{2})$ .

Referring now to FIG. 3C, with a switching pattern set in accordance with the third row of Table 1, the switched-capacitor circuit 30 provides a step down ratio of two-thirds (24)

It should be appreciated that the maximum voltage to which any of the devices in transformation stage 30 will be exposed is  $\frac{2}{3}$  of the input voltage (V<sub>1</sub>) and some of the devices may see less ( $\frac{1}{2}$ V<sub>1</sub> and  $\frac{1}{3}$ V<sub>1</sub>) depending upon a selected operating mode. It should be appreciated that all of the devices in transformation stage 30 must be able to block the required voltage to realize all three step-down ratios. For example, M<sub>1</sub> must be rated to block  $\frac{2}{3}$ V<sub>1</sub>, however it only sees  $\frac{1}{2}$ V<sub>1</sub> for a step-down ratio of  $\frac{1}{2}$  and  $\frac{2}{3}$  If more complicated networks are used (i.e. more switches), it may be possible to realize the same functionality at higher efficiency, but at the cost of area.

The switched capacitor stage 30 is thus controlled to maintain the intermediate voltage  $V_x$  within a specified (narrow) range (or window) of voltages as the input voltage varies across a wide range of voltages. The size, maximum voltage 65 and minimum voltage of the output window of the SC transformation stage can be tailored to fit the regulation stage.

ing but not limited to how charge flows in the circuit and how much loss is generated by a particular pattern.

As is understood in the art, the circuit topology and switching patterns are selected such that charge balance is maintained on the charge storage elements (e.g. capacitors), which imposes a rational conversion ratio between the input and the output charge (and current) for a given switching pattern. This conversion ratio is the inverse of the ideal voltage conversion ratio of the circuit for a given switching pattern. In region 32, a transformation ratio of 2/3 is used while in region 34 a transformation ratio of ½ is used while in region 36 a transformation ration of 1/3 is used. It should be appreciated that the waveform of FIG. 4 is selected strictly on  $V_{I\!N}$ , but it should be appreciated that the selection could be made based upon both  $V_{IN}$  and  $V_{OUT}$ . For example, one might select the switching pattern transitions and hence the intermediate voltage window so that the regulation stage can operate near a desired conversion ratio, maximizing efficiency.

The regulating stage can be implemented with numerous topologies for very low output voltages (e.g. sub 1 V); good options include a synchronous buck converter, cascodeswitch synchronous buck converter, interleaved synchronous buck converter, three-level synchronous buck converter, and four-switch "buck-boost" converter. Very fast transistors, such as base CMOS transistors in an integrated process, can be used in the regulation stage since the input voltage is quite low. This allows the regulation stage to operate at a very high switching frequency, which in turn reduces the size of its passive components.

One option to achieve a very high degree of integration is to fabricate the converter in a multiple-voltage monolithic process (e.g., a process providing for extended drain transistors). The switched capacitor stage can be implemented with higher voltage devices and operated at a relatively low frequency (e.g., 1 MHz) commensurate with the high-voltage devices. The regulating stage can be implemented with low-voltage devices, and thus can be operated at considerably higher frequencies (e.g., 100 MHz), providing small volume for the passive components and fast regulation. Alternatively, multichip fabrication can be used in which the two stages are implemented in different processes, each optimized for their respective functions.

A converter with a large input voltage range and output current range can thus be realized if a reconfigurable switched capacitor converter with multiple transformation ratios is

used as a transformation stage along with a high frequency, low voltage regulation stage. The converter can also take advantage of state-of-the-art CMOS processes that have additional high voltage devices.

The energy loss  $E_L$  associated with charging a capacitor C 5 from zero to a voltage V with a series connection from a dc voltage source of value V is ½ CV<sup>2</sup>, and is independent of the parasitic series resistance (R). Furthermore, for a conventional SC circuit, a fixed amount of charge-up energy loss equal to  $\frac{1}{2}$  C  $\Delta V^2$  will result at each switch interval, where  $\Delta V$ corresponds to the difference between the initial and final value of the capacitor voltage. It is important to note that this fixed charge-up loss cannot be reduced by employing switches with lower on-state resistance. It is for this reason that conventional SC converters aim to minimize the variations of the voltage on the capacitors during the charging phase and only operate efficiently at certain conversion ratios. Consequently, conventional SC converters require relatively large capacitors to achieve high efficiency and power levels and do not provide efficient regulation from variable input 20 voltages. As is shown below, a second embodiment of a power converter circuit permits more efficient use of the capacitors, enabling reduction in the required capacitor size and/or improvement in system efficiency. Furthermore, the second embodiment does not require a reconfigurable switched-ca- 25 pacitor network although it may use one.

To understand the approach used in the second embodiment, consider the circuit of FIG. 5 which is a simple example, which illustrates the loss-mechanism for charging of the capacitors in the switched capacitor stage. FIG. 5 is 30 used to explain an example of the charging process of a capacitor C, where a resistor R represents the combined equivalent series resistance (ESR) of the capacitor and switch on-state resistance. The capacitor has an initial charge of V<sub>i</sub>, and the switch is closed at  $t=0^+$  After  $t=0^+$ , the difference 35 between voltage  $V_{in}$  and the capacitor at each instance in time appears across the parasitic resistor R resulting in dissipation during charging. If charging is allowed to continue for a sufficient period of time, the voltage across the capacitor will charge up to  $V_{in}$ , and the voltage across the resistor will 40 become 0 V. The voltage across the resistor and the current through it, results in a power loss during the charging phase of the capacitor, which depends on the capacitance and the net charge in the capacitor. It is this loss which limits the efficiency of the switched capacitor stage.

FIG. 5A illustrates a technique to improve the charge-up efficiency of the switched capacitor circuit. In this embodiment, an auxiliary converter 40 operating at a much faster switching frequency than the switched capacitor stage is used to reduce the energy loss of the switched capacitor circuit. 50 The switching frequency of the auxiliary converter should be sufficiently higher than the switched capacitor stage such that the capacitor charging takes place over many switching cycles of the auxiliary converter. A factor of five in switching frequency may be sufficient for this purpose, and factors of 55 ten or more are typical.

The auxiliary converter 40 may be the regulating converter used to supply the output, or it may be a separate converter. The system is designed such that the majority of the difference between the input voltage  $V_{in}$  and the capacitor stack voltage  $V_{C}$  appears across the input of the auxiliary converter when the capacitor is charging. Instead of being dissipated as heat in the resistor, the energy associated with charging the capacitor stack is delivered to the output of the auxiliary converter.

FIG. 6 illustrates a possible implementation of the general embodiment discussed above in conjunction with FIG. 5.

14

Referring now to FIG. 6, a power converter 50 includes a transformation stage 52 and an auxiliary converter and the regulating converter stage 54. Transformation stage 52 includes a plurality of capacitors C1, C2 and a first group of switches (each labeled S1) and a second group of switches (each labeled S2). Auxiliary converter and the regulating converter stage 54 includes a plurality of capacitors  $C_{small}$ ,  $C_{buck}$ , a plurality of switches S3, S4 and an inductive element  $L_{buck}$ .

In the exemplary embodiment shown in FIG. 6, a "fast regulating converter" (in this case a synchronous buck converter) serves as both the auxiliary converter and the regulating converter stage 54 for the system 50. Auxiliary converter and the regulating converter stage 54 operates at a switching frequency much higher than that of the switched capacitor stage 52. As the capacitor  $C_{small}$  serves only as a filter and bypass for the fast regulating converter, its numerical value can be much smaller than the capacitors  $C_1$  and  $C_2$  of the switched capacitor transformation stage. When the switchedcapacitor stage is configured for charging of C1 and C2 (switches S1 closed), the difference between  $V_{\it in}$  and the sum of the voltages across capacitors C<sub>1</sub> and C<sub>2</sub> appears across the input terminal of the fast regulating converter. C<sub>1</sub> and C<sub>2</sub> thus charge with low loss, and at a rate determined by the power drawn from the regulating converter to control the system output. Likewise, when the switched-capacitor stage is configured for discharging C<sub>1</sub> and C<sub>2</sub> in parallel (switches S2 closed), the discharge is at a rate based on the power needed to regulate the output.

In operating the system, the switched capacitor stage 52 can be switched (switch sets S1 and S2 on alternately) such that the voltage  $V_x$  at the input of the fast regulating converter stays within a specified window or below a specified voltage. For example, the switches could be controlled such that the capacitor  $C_1$  and  $C_2$  voltages remain within a specified hysteresis band about  $V_{in}/3$ , such that the regulating converter sees a maximum input voltage near  $V_{in}/3$ . Alternatively, the switched capacitor stage can be controlled to provide a specified maximum voltage  $V_x$  at the input of the auxiliary converter.

Referring now to FIG. 7, a plot of switch configuration vs. voltage illustrates a control strategy utilizing the above-described technique, where two separate reference voltages are used to ensure that the input voltage of the auxiliary converter does not exceed  $V_{X,max}$ . In this example, the switches designated by reference number 1 in FIG. 6 are on or closed (series charging of the capacitors) until  $V_X$  falls below  $V_{re/1}$ . At this time, switches 1 turn off or open, and the switches designated with reference numeral 2 turn on (parallel discharging of capacitors), until  $V_X$  falls below  $V_{re/2}$ , at which time the cycle repeats. The reference voltages are set by the maximum auxiliary input voltage  $V_{X,max}$ , and are given by:

$$V_{ref1} = V_{IN} = 2V_{X,mas} \ V_{ref2} = \frac{V_{in} - V_{X,max}}{2}$$

It should be understood that the topology of the fast regulating converter (a buck converter in the example of FIG. 6)

can be any type of power converter that is able to provide fast

switching and efficient regulation of the output voltage for

various input voltages (synchronous buck, three-level synchronous buck, SEPIC, soft switched or resonant converter,

etc.). Similarly, the switched-capacitor circuit can be realized

with a variety of topologies, depending on desired voltage

transformation and permitted switch voltages.

Referring now to FIG. 8, yet another embodiment of a power converter circuit is shown. The circuit topology shown in FIG. 8 illustrates how the auxiliary converter can be used as a separate energy-recovering device, with an independent output voltage. In this embodiment, two parallel switchedcapacitor circuits are employed, operating in anti-phase. When the capacitors of step-down cell 1 are charging in series (switches A closed, switches B open), the capacitors of cell 2 are discharging in parallel. The difference between the input voltage and the sum of the charging capacitors appears across the input terminal of the auxiliary converter. The charging energy can again be recovered by this auxiliary converter, providing a means for improving overall efficiency or increasing power density. It is important to note that the output voltage of the switched-capacitor stage,  $\mathbf{V}_{out1}$ , can be  $\,$  15 regulated using the auxiliary converter. The auxiliary converter performs the regulating functions in a manner similar to some (lossy) current-controlled strategies. The auxiliary converter can again be any type of fast regulating converter, just as in the example of FIG. 6. The regulated output voltage 20  $V_{\it out2}$  can be higher or lower than  $V_{\it out1}$ , depending on the choice of auxiliary converter. This voltage can be used for a variety of purposes. Examples include, but are not limited to: powering the SC transistors, fed back to the input, delivered to the output, or providing a separate output voltage for appli- 25 cations where that is desirable. R<sub>toad</sub> in this circuit can represent the actual load, or may represent the input impedance of another converter or set of converters for regulating system outputs.

Having described one or more preferred embodiments of 30 the circuits, techniques and concepts described herein, it will now become apparent to those of ordinary skill in the art that other embodiments incorporating these circuits, techniques and concepts may be used. Accordingly, it is submitted that that the scope of the patent should not be limited to the 35 described embodiments, but rather, should be limited only by the spirit and scope of the appended claims.

What is claimed is:

- 1. A converter circuit comprising:

- a switched capacitor transformation stage having a transformation stage input port and a transformation stage output port, said switched capacitor transformation stage comprising one or more switches and one or more capacitors and said switched capacitor transformation stage configured to accept an input voltage  $V_{IN}$  at the 45 transformation stage input port and provide an intermediate output voltage at the transformation stage output port:

- an auxiliary converter stage having an input coupled to said switched capacitor transformation stage, said auxiliary 50 converter stage comprising one or more switches and one or more magnetic energy storage components configured to recover energy normally dissipated in capacitors of said switched capacitor transformation stage via said one or more magnetic energy storage components; 55 wherein in response to the one or more switches of said switched capacitor transformation stage being config-

16

ured so that a capacitor in said switched capacitor transformation stage is charging or discharging, said switched capacitor transformation stage operates such that a portion of the difference between the input voltage  $V_{I\!N}$  and a capacitor stack voltage  $V_c$  appears across the input of said auxiliary converter stage and said auxiliary converter stage recovers energy normally dissipated when charging or discharging capacitors of said switched capacitor transformation stage;

wherein the portion of the difference between the input voltage VIN and the capacitor stack voltage  $V_c$  corresponds to a majority of the difference between the input voltage  $V_N$  and the capacitor stack voltage  $V_c$ ;

wherein said one or more switches in said auxiliary converter stage operate at a switching frequency which is higher than the switching frequency of the one or more switches in said switched capacitor transformation stage.

- 2. The converter circuit of claim 1 wherein the input of said auxiliary converter stage is provided having an apparent input resistance which is higher than an equivalent series resistance of said switched-capacitor transformation stage.

- 3. The converter circuit of claim 1 wherein at least one of said one or more magnetic energy storage components comprises an inductive element.

- **4**. The converter circuit of claim **1** wherein said switched capacitor transformation stage is provided as a reconfigurable switched capacitor transformation stage which provides power conversion at multiple distinct conversion ratios.

- 5. The converter circuit of claim 1 wherein said switched capacitor transformation stage provides power conversion as a function of at least one of: an input voltage  $V_{I\!N}$ , a reference voltage, the intermediate voltage, and an output voltage.

- **6.** The converter circuit of claim **1** wherein in response to said one or more switches in said switched capacitor transformation stage being configured so that the capacitor is charging, the input voltage  $V_{I\!N}$  and the capacitor stack voltage  $V_c$  appears across the input of said auxiliary converter stage.

- 7. The converter circuit of claim 1 wherein in response to said one or more switches of said switched capacitor stage being configured such that a capacitor in said switched capacitor transformation stage is discharging, said switched capacitor transformation stage operates such that a portion of the difference between the input voltage  $V_{I\!N}$  and a capacitor stack voltage  $V_c$  appears across the input of said auxiliary converter stage.

- 8. The converter circuit of claim 1 wherein said switched capacitor transformation stage operates such that a portion of the difference between the input voltage  $\mathbf{V}_{I\!\!N}$  and a capacitor stack voltage  $\mathbf{V}_c$  appears across the input of the auxiliary converter stage in response to a change in charge in at least one capacitor of said switched capacitor transformation stage.

\* \* \* \* \*